www.Vidyarthiplus.com

### Basics of Operational Amplifiers UNIT – I

# CONTENTS

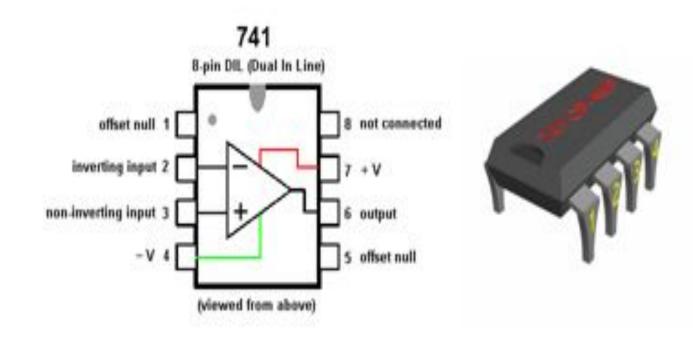

Operational Amplifiers

- Basic Informations (IC741)

- Characteristics of Ideal Op-Amp

- Operational Amplifier Stages

- Internal circuits of IC741

- DC and AC Characteristics (Slew rate)

- Open and Closed loop configurations

- **BJT** Differential Amplifier

Current Mirror, Current sources(Widlor and Wilson)

Voltage sources

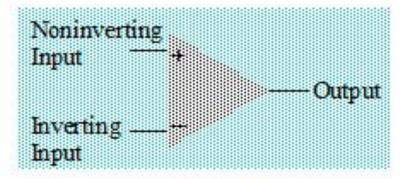

#### Operational Amplifier (Op-Amp)

- · Very high differential gain

- High input impedance

- Low output impedance

- Used in oscillator, filter and instrumentation

- Accumulate a very high gain by multiple stages

#### www.Vidyarthiplus.com

#### Common-Mode Operation

- Same voltage source is applied at both terminals

- Ideally, two input are equally amplified

- Output voltage is ideally zero due to differential voltage is zero

- Practically, a small output signal can still be measured

#### Common-Mode Rejection Ratio (CMRR)

Differential voltage input :  $V_d = V_+ - V_-$

Common voltage input :  $V_c = \frac{1}{2}(V_+ + V_-)$

Output voltage :

$V_o = G_d V_d + G_c V_c$

G<sub>d</sub>: Differential gain G<sub>c</sub>: Common mode gain

Common-mode rejection ratio:  $CMRR = \frac{G_d}{G_e} = 20\log_{10}\frac{G_d}{G_e}(dB)$

EC6404-LINEAR INTEGRATED CIRCUITS-ECE DEPT-SVCE www.Vidyarthiplus.com

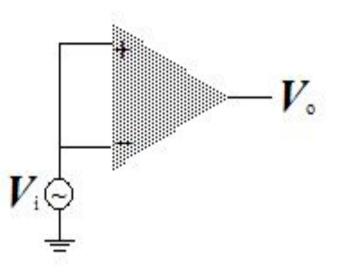

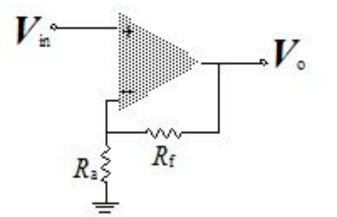

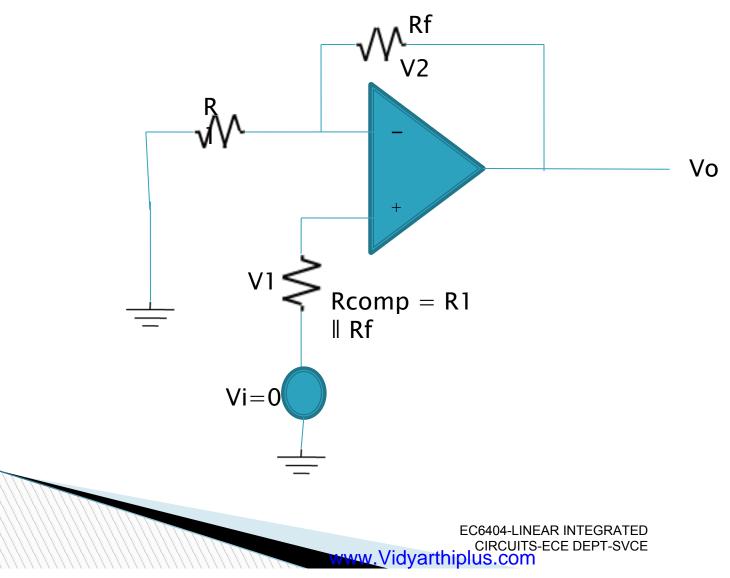

#### Noninverting Amplifier

- (1) Kirchhoff node equation at  $V_+$ yields,  $V_+ = V_i$

- (2) Kirchhoff node equation at  $V_{-}$ yields,  $\frac{V_{-}-0}{R_{a}} + \frac{V_{-}-V_{a}}{R_{f}} = 0$

$V_+ = V_-$  yields

$$\frac{V_i}{R_a} + \frac{V_i - V_o}{R_f} = 0 \quad \text{or} \quad \frac{V_o}{V_i} = 1 + \frac{R_f}{R_a}$$

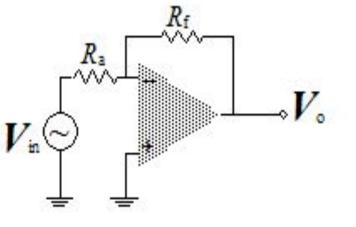

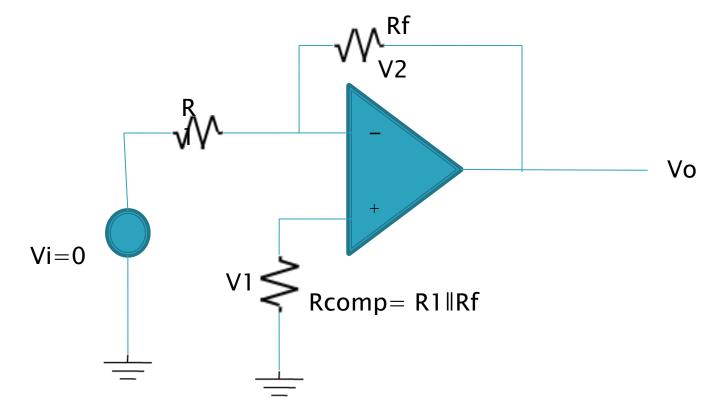

#### Inverting Amplifier

- (1) Kirchhoff node equation at  $V_+$ yields,  $V_+ = 0$

- (2) Kirchhoff node equation at  $V_{-}$ yields,  $\frac{V_{ie} - V_{-}}{R_{a}} + \frac{V_{a} - V_{-}}{R_{f}} = 0$

$$V_{+} = V_{-}$$

yields

$$\frac{V_{o}}{V_{in}} = \frac{-R_{f}}{R_{a}}$$

I

www.Vidyarthiplus.com

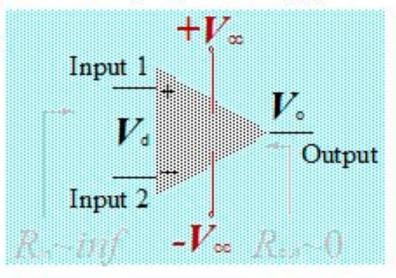

#### Characteristics of Ideal Op-Amp

- For an ideal Op-Amp, V<sub>1</sub> = V<sub>2</sub> = 0 and hence

I<sub>1</sub> = i<sub>2</sub> = 0

- Open loop voltage gain  $A_{OL} = \infty$

- Input Impedance  $R_i = \infty$

- Output Impedance  $R_o = 0$

- Bandwidth BW  $= \infty$

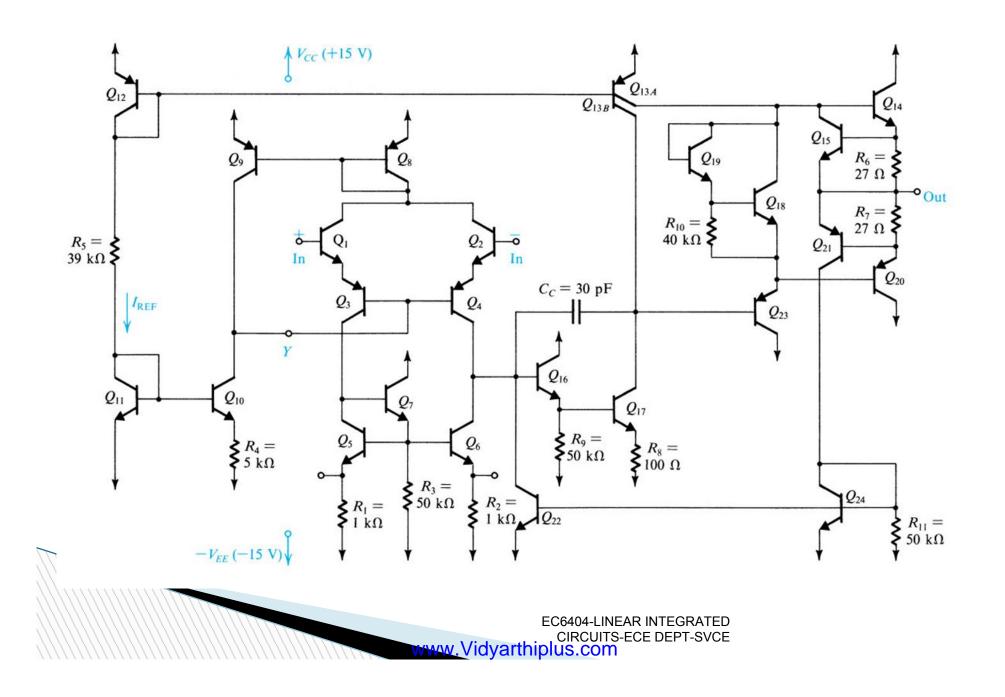

# Stages and Internal circuit of general Op-Amp (IC 741)

General Stages

- Input Stage

- Intermediate Stage

- Buffer and Level Shifting Stage

- Output Stage

#### The Input Stage

- The input stage consists of transistors Q1 through Q7.

- Q1-Q4 is the differential version of CC and CB configuration.

- High input resistance.

- Current source (Q5-Q7) is the active load of input stage. It not only provides a high-resistance load but also converts the signal from differential to single-ended form with no loss in gain or common-mode rejection.

#### The Intermediate Stage

- The intermediate stage is composed of Q<sub>16</sub>, Q<sub>17</sub> and Q<sub>13B</sub>.

- Common-collector configuration for Q<sub>16</sub> gives this stage a high input resistance as well as reduces the load effect on the input stage.

- Common-emitter configuration for Q<sub>17</sub> provides high voltage gain because of the active load Q<sub>13B</sub>.

- Capacitor Cc introduces the miller compensation to insure that the op amp has a very high unitgain frequency.

#### Level Shifting Stage

- All stages coupled to each other, hence voltage level of previous stage applied to next stages.

- So stage by stage d.c level increases, such high voltage drives the transistors into saturation

- Hence before output stage, it is necessary to bring such high voltage to zero volt.

- Level shifter brigs the d.c level down to ground potential when no signal is applied

- The buffer is an emitter follower whose input impedance is very high.

#### The Output Stage

- The output stage is the efficient circuit called class AB output stage.

- Voltage source composed of Q<sub>18</sub> and Q<sub>19</sub> supplies the DC voltage for Q<sub>14</sub> and Q<sub>20</sub> in order to reduce the cross-over distortion.

- Q<sub>23</sub> is the CC configuration to reduce the load effect on intermediate stage.

- Short-circuit protection circuitry

- Forward protection is implemented by R<sub>6</sub> and Q<sub>15</sub>.

www.Vidvarthiplus.com

Reverse protection is implemented by R<sub>7</sub>, Q<sub>21</sub>, current source(Q<sub>24</sub>, Q<sub>22</sub>) and intermediate stage.

CIRCUITS-ECE DEPT-SVCE

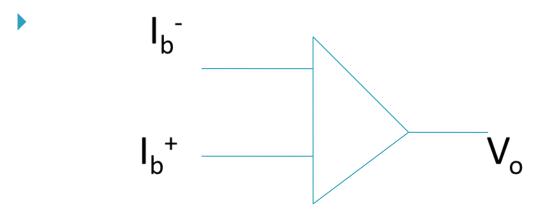

# **DC Characteristics**

- Input Bias Current (I<sub>b</sub>)

- Input Offset Current(I<sub>os</sub>)

- Input Offset Voltage (V<sub>ios</sub>)

- Thermal Drift

#### **Input Bias Current**

Bias Current I<sub>B</sub> =

$$\frac{I_b^+ + I_b^-}{2}$$

#### Bias Current Compensation in Inverting mode

#### Bias Current Compensation in Non Inverting mode

# Input Offset Current

Input Offset current will work if both bias currents are equal.

If they are not equal, the difference between them is know as Input Offset current

$$\mathbf{I}_{\rm os} = \mathbf{I}_{\rm b}^+ - \mathbf{I}_{\rm b}^-$$

# Input Offset Voltage

Due to unavoidable imbalances inside the opamp, the output voltage will not be zero with zero input voltage. This voltage is called as

input offset voltage.

Considering this voltage V<sub>ios</sub>,

Output Voltage V<sub>o</sub> =  $(1 + \frac{R_f}{R_1})V_{ios}$

# **Thermal Drift**

- Bias current, Offset current and Offset voltages change with temperature. This change is called as drift.

- Offset current drift is expressed in nA/°C

- Offset voltage drift is expressed in mV/°C

- To avoid this drift careful printed circuit board layout must be used and forced air cooling may be used to stabilize the ambient temperature.

#### AC Characteristics (Slew Rate - SR)

The maximum rate of change of output voltage caused by step input voltage, specified in V/µs

Cause of SR:

There is a **capacitor** within an op-amp which prevent the output voltage from responding immediately to a fast change in input. This capacitor caused the SR

$$\frac{dv_o}{dt} = V_m \, \dot{\psi} \, \cos \dot{\psi} t$$

The maximum rate of change occurs when  $\cos\psi t = 1$ Therefore SR =  $(dv_o/dt)$ max =  $\psi V_m$ Or SR =  $2\pi f V_m V/s$

Or SR =

$$\frac{2\pi f V_m}{10^6}$$

V/µs

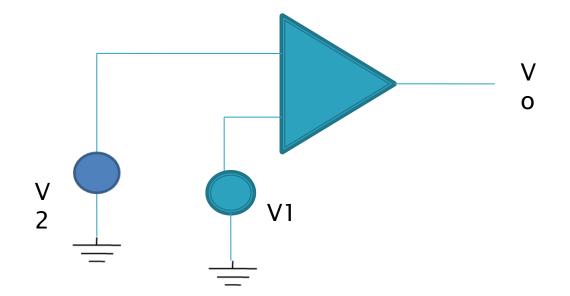

### **Open Loop Operation**

# **Open loop operation**

- Simplest way of operation in op-amp

- V<sub>1</sub> and V<sub>2</sub> applied to non-inverting and inverting terminals respectively

- Vo will be either at positive saturation or negative saturation as V<sub>1</sub> × V<sub>2</sub> or V<sub>2</sub> × V<sub>1</sub> respectively

- Hence amplifier acts as switch only

- Applications as voltage comparator, zero crossing detector.

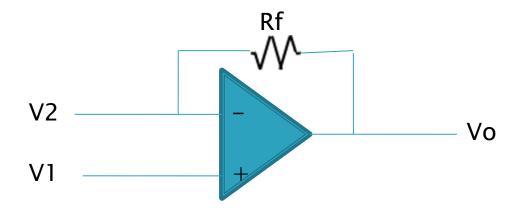

### **Closed Loop Operation**

# **Closed loop Operation**

- Mostly used configuration

- The feedback allows to feed the some part of output back to input

- The feedback is said to be negative as the resistor connects the output to inverting terminal

- Closed loop gain is much less than Open loop gain

- It reduces the possibility of distortion, increases the BW.

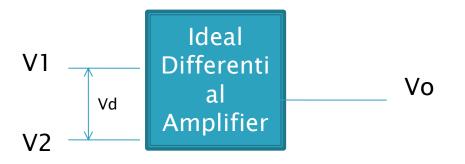

# **Differential Amplifier**

Amplifies the difference between two input voltages. ( $V_d = V_1 - V_2$ )

$$V_o$$

$q$  (V<sub>1</sub>−V<sub>2</sub>)

$V_o = A_d(V_1-V_2)$  where  $A_d = Differential Gain$

$V_o = A_dV_d$ , hence  $A_d = V_o/V_d$

$A_d = 20 \log A_d$  (dB)

# Common Mode Gain

- If two input voltages are equal , it is common mode

- Then common mode voltage  $V_c = (V_1 + V_2) / 2$

- Now output voltage  $V_o = A_c V_c$

- Total voltage for any differential amplifier is  $Vo = A_dV_d + A_cV_c$

- $\mathbf{F} CMMR = A_d / A_c \text{ (or) } 20 \text{ log } (A_d / A_c) \text{ dB}$

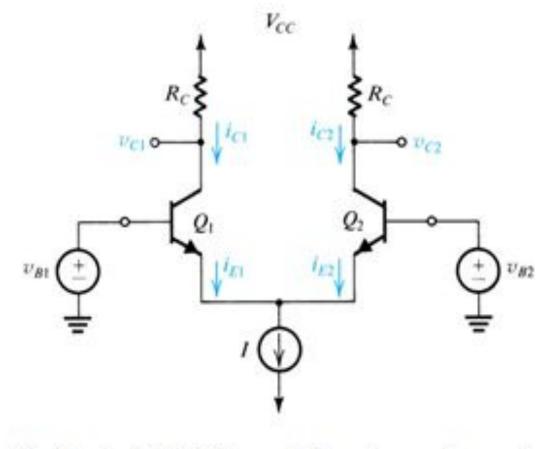

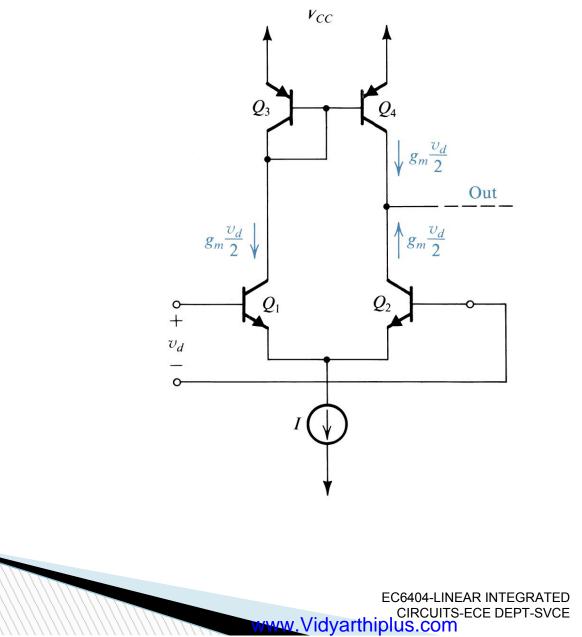

#### **BJT Differential Amplifier**

The basic BJT differential-pair configuration.

www.Vidyarthiplus.com

# **Difference Mode Operation**

- Q1 positive going, Q2 negative going signal

- Hence there will be negative going output at the collector of Q1 and positive going output at the collector of Q2

- So the difference between two voltages Vo is the twice as large as the signal voltage.

#### www.Vidyarthiplus.com

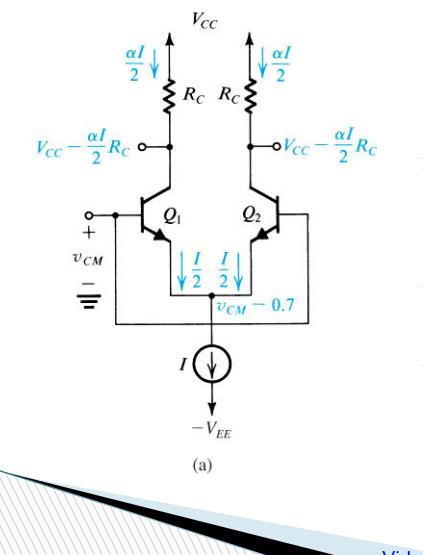

#### **Common Mode Operation**

The differential pair with a commonmode input signal  $V_{CM}$ .

≻Two transistors are matched.

≻Current is divided equally between two transistors.

> The difference in voltage between the two collector is zero.

#### Configurations of Differential Amplifier

- Dual input , balanced output

- Dual input, unbalanced output

- Single input, balanced output

- Single input, unbalanced output

#### Note:

If output is taken between two collectors – balanced output

If output is taken between one collector with respect to ground then it is unbalanced output

#### **D.C Analysis of Differential Applying KVL to base-emitter loop,** $-I_RR_S - V_{RE} - 2I_ER_E + V_{EE} = 0$ -----(1)

But,  $I_c = \beta I_B$  and  $I_c \approx I_E$ Therefore,  $I_B = I_E / \beta$  -----(2)

(2) In (1) we get,

$$[-I_{E}R_{S}/\beta] - V_{BE} - 2I_{E}R_{E} + V_{EE} = 0$$

$$I_{E}[(-R_{S}/\beta) - 2R_{E}] + V_{EE} - V_{BE} = 0$$

-----(3)

Therefore

In practical,

$R_{s}/2R_{E}$ , hence  $I_{E} = [V_{EE}-V_{BE}]/2R_{E}$  -----(5)

EC6404-LINEAR INTEGRATED CIRCUITS-ECE DEPT-SVCE CIRCUITS-ECE DEPT-SVCE The collector voltage of Q1  $V_c = V_{cc} - I_c R_c$  -----(5) And  $V_{CE} = V_c - V_E = (V_{CC} - I_C R_C) - (-V_{BE})$   $V_{CE} = V_{CC} + V_{BE} - I_C R_C$  -----(6) For the differential amplifier, The operating point values  $V_{CEQ} \approx V_{CE}$ And  $I_{CO} \approx I_E$

#### www.Vidyarthiplus.com

Differential Amplifier with active load

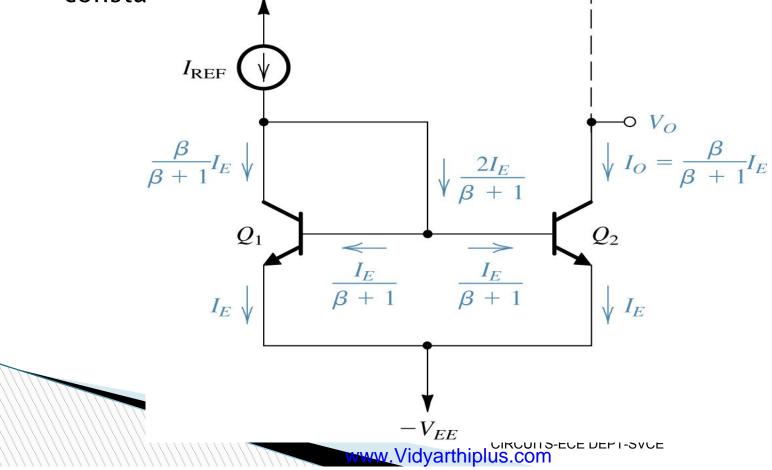

# **Current Mirror Circuit**

A current mirror is a circuit designed to copy a current through one active device by controlling the current in another active device of a circuit, keeping the output current constant regardless of loading

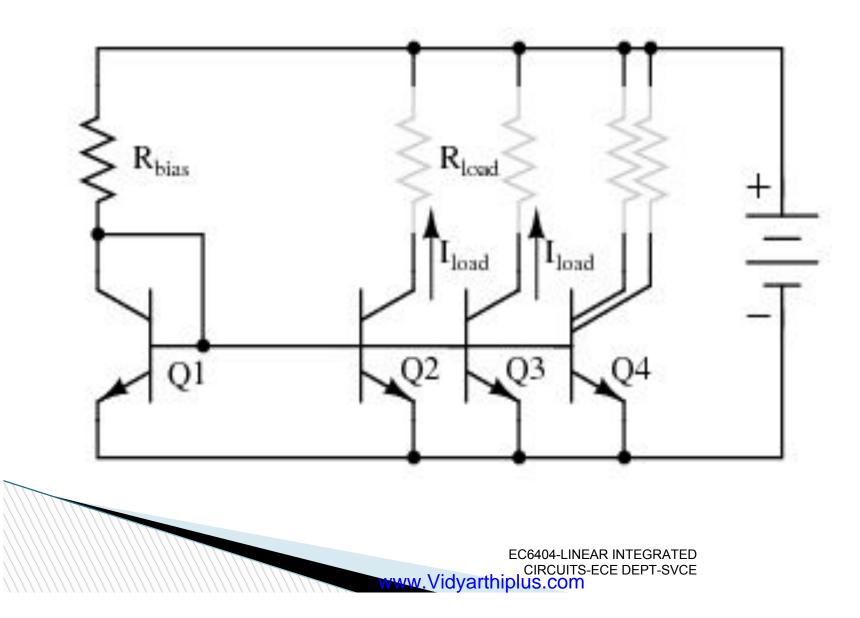

#### **Multiple current mirror**

#### The Wilson current source

An improved circuit, called Wilson current source, with higher output impedance that the previous current mirror.

For the Wilson current source, the following

www.Vidyarthiplus.com

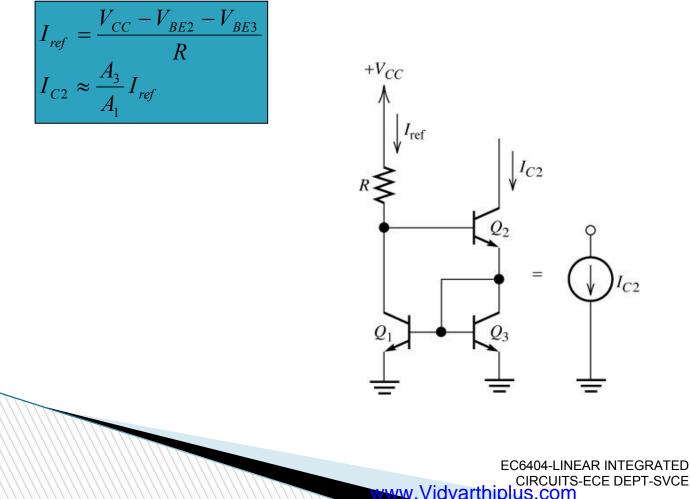

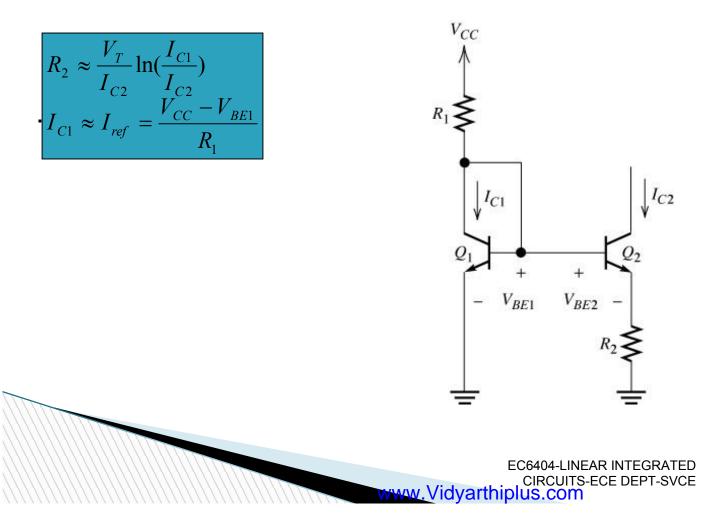

#### The Widlar current source

When the desired current is small, the Widlar current source may be a better alternative, as shown in the Figure.

For Widlar current source,

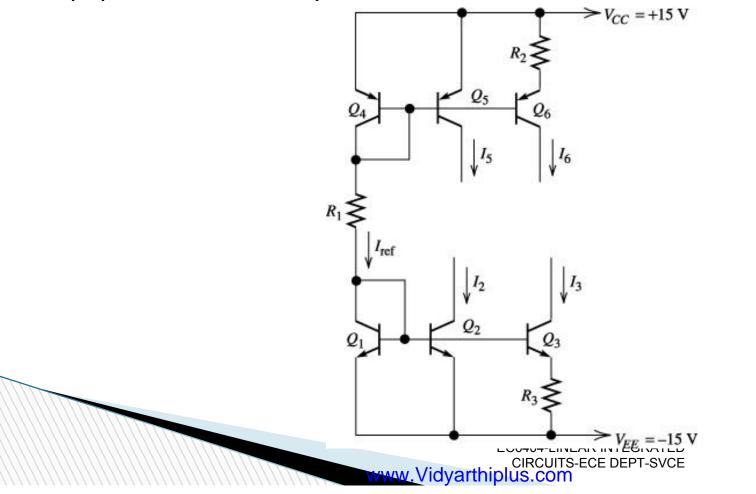

#### The combined current sources

In an Integrated Circuit amplifier, several current sources use the same reference current, as shown below.

The current through R1 is the reference current for all four current sources. Q1, Q2 forms a current mirror, and Q1, Q3 forms a Widlar source. Notice the pnp current source by Q4, Q5 and Q6.

# Voltage Reference Circuits

- Used to provide a constant d.c voltage, which acts as a reference for other circuits

- It is independent of changes in the parameters like temperature, input line voltage and load current

- Accuracy and stability with temperature are the basic characteristics of any voltage reference circuit

UITS-ECE DEPT-S\

• Temperature coefficient TC =  $\Delta Vo/\Delta T$  in mV/<sup>0</sup>C

Www.Vidvarthiplu

• % of temperature coefficient

%TC = 100

$$\left[\frac{\Delta Vo/Vo}{\Delta T}\right]$$

in %/<sup>0</sup>C

#### Performance parameters of Voltage reference circuits

- Line regulation (Input/Supply regulation) Line Regulation =  $\frac{\Delta v_o}{\Delta v_i}$

- Load regulation

Load Regulation =  $\frac{\Delta v_o}{\Delta I_I}$

• Long term stability

The ability of circuit to maintain the output voltage constant with respect to time

• Ripple Rejection Ratio (RRR)

$$\mathsf{RRR} = 20 \log \frac{v_{ri}}{v_{ro}}$$

### Problems

- > Design an amplifier with a gain of -10 and input resistance equal to  $10 \ {\rm K}\Omega$

- For an op-amp with  $R_1=10K\Omega$  and  $R_2=100K\Omega$ is given  $v_i=1V$ . A load  $25K\Omega$  is connected to the terminal. Calculate  $i_1, V_o, i_L$  and total current  $i_o$  into the output pin.

- Design an amplifier with a gain of +5 using op-amp.

- For an op-amp circuit,  $R_1 = 5k\Omega$  and  $R_f = 20k\Omega$ with  $v_i = 1V$ . A load resistor of  $5k\Omega$  is connected at the output. Calculate  $V_o$ ,  $A_{CL}$ ,  $i_L$ and  $i_o$ .