### UNIT-V SAMPLING GATES

Basic operating principles of sampling gates, unidirectional diode gate, Bi-directional sampling gates using transistors, Reduction of pedestal in gate ciraint, four diode sampling gate, an alternate form of four diode gate, six diode sampling gate, chopper amplifier, sampling scope.

#### LOGIC FAMILIES

Realization of Logic gates (or, AND, Not) using Diodes and Transistors, DCTL, RTL, DTL, TTL, ECL, CML, CMOS logic family and comparison of logic families.

#### SAMPLING GATES

#### Introduction

Def:

"An ideal sampling gate is a transmission of an input wave form during a reproduction of an input wave form during a solected time interval and is zero otherwise".

The time interval for transmission is selected by an externally improcessed signal which is called the gating signal.

The gating signal is also called as control pulse (00) selector pulse (00) Enabling Pulse.

-> Sampling gates are also called as toansmission gates (00) time-selection circuits er, linear gases.

classification of sampling gates:

These are broadly classified as

- i) unidisectional sampling gates.

- 2) Bi-directional sampling gates.

Unidisectional sampling gave:

Et the input signal consists cesentially of a unidisectional pulse, the sampling gate is required to respond to an input signal of only one polarity, such sampling gate is known as unidirectional gate.

Bi-disectional sampling gave:

If a sampling gate is sequised to handle (or townsmit) the excursions of signals of both the polarities, it is known as Bi-Dischional sampling gate.

A sampling gate has one signal input and during the selected time interval, the output must reproduce faithfully the input wave form, be it a pulse, a sinusoid or any other wave form, Hence a sampling gate is also called as linear gate.

# compasison between Logic gue and sampling gave

#### logic gate

- i) In this, there can be any number of inputs.

- at the output a pulse cost no pulse, depending on the pulses present at the namy gate inputs and the type of the gate.

- 3) Ex: AND, OR, NOT, NAND, NOR, EX-OR

#### sampling gates

- i) In this, it has only single input.

- 2) A sampling gate

poovides an output,

which is an exact

sepooduction of the

input during the

input during the

(whatever may be the

input, a pulse,

a sinusoid or any

other wave from.

- 3) Ex: unidirectional and Bi-directional compling gates.

In fig (a), switch 's' is normally open and is closed during the desired transmission internal.

-> In fig (b), switch 's' is normally closed and is opened only during the decided to ansmission interval.

Semiconductor devices such as diodes and they toansistoos are used as switches when they are conducting, they acts as a closed switch and whey they are not conducting, they are not conducting, they are and whey they are not conducting, they are and whey they are not conducting, they are and open switch.

-> Edeally, the switches should have zero registance when when closed and infinite registance when open.

But semiconductor devices do not have infinite back seeistonce and their forward registonce may lie in the sange of several ohms.

When such devices are used there is no

generally apparent advantage in either

the sesses (00) Shund switch position, and the decision with respect to the circuit of choice must depend on the pasticular application.

-> when semiconductor devices are used as a switch the circuit of fig (a) has the following disadvantages over the circuit of fig (b) are:

- a) The inevitable stray capacitance across the switch will permit some signal transmission even when the switch is open.

- b) Since the signal is toansmitted through s' those will be some attenuation and distostion introduced by the non-linearity of the device used for the switch.

A uni-disectional sampling gate which uses a semiconductor diode as a switch is shown below:

Signal I RIS RL Vo

Control

Signal - 2 I fig: unidirectional diode gate

The above gate is suitable for a positive going input signal.

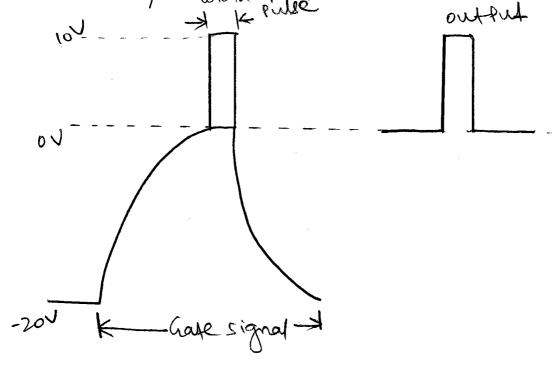

The gate signal i.e; the signal which determined the gating (00) townsmission period, is a sectangular wave from with voltage levels.

-v, and -vz is applied and voltage level.

-v, is more positive than -vz.

when the gotting signal is at -1/2 the diode gets reverse-biased so there is no conduction because of apacitive coupling, the signal input voltage will appear at the signal input voltage will appear and point A with an average level -1/2 and home resulting zero output.

It is assumed that the peak amplitude of the input signal is smaller than the back-biasing voltage - 1/2.

If the peak amplitude of the input signal is greater than the voltage level - 1/2, the diode may conduct giving under table output voltage.

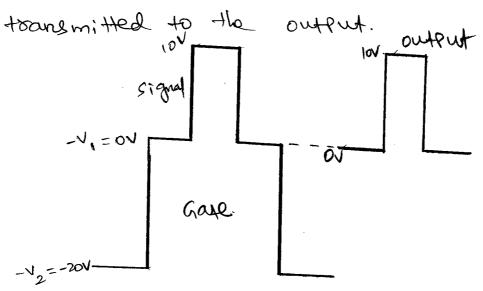

when the gate signal voltage of see aboutly from -V2 to -V1, the Positive going input signal causes the diode to be forward biased, diode D conducts and a time-coincident signal input Pulse is towns mitted through the gase and an output voltage appears across RL.

If ideal conditions are assumed, then there is neither attenuation nor distortion of the input signal. The output voltage would be an exact replica of the input signal.

-> The effect of the higher level of the gating signal -V, on gate output is shown below.

by the input signal is a +100 pulle,

observed by the output is a

time of the output is a

over the output

operation in this manner is often advantageous when the base line of the input signal has some noise signal superimposed.

The level -V, may be adjusted so that only that past of the signal above the noise threshold appears at the output.

when used in this manner, the circuit is called as "Threshold gare".

townsmitted to the output.

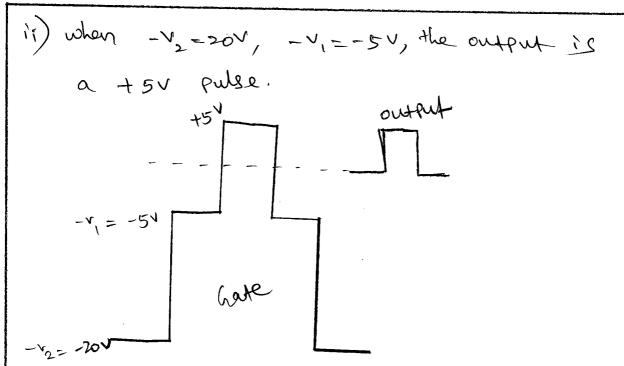

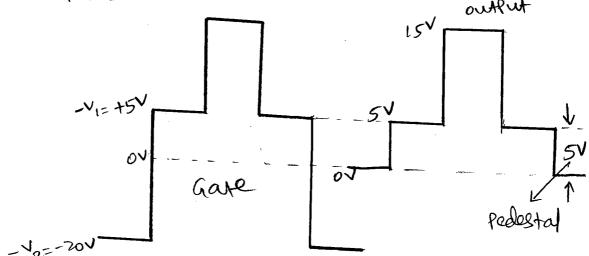

iv) when  $-v_2 = -20V$  and  $-v_1 = +5y$ , then the output is a +100 pulse superimposed on a pedastal of +5V

The wave forms of the above tigues as not practical, because we have not considered the fact that Ric, network constitutes an integrating

network for the gate wave form.

Hence the gate voltage will not appear aboutly at A as segurored, but sather will of se exponentially with a time constant Ric, and fall at similar sale.

Hence this type of gate is not Surtable for selecting a past of a continuous wavestron.

However if the input signal is a pulse whose width is very small as compared to the gare width, the input may be toansmitted the gare width, the input may be toansmitted satisfactory at the output as is shown blow. Satisfactory at the output as is shown blow. I width of input output

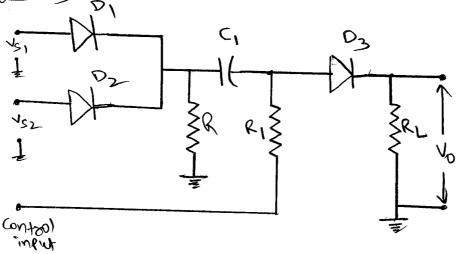

Uni-distational diode gate for most than one input signal The uni-Disectional Sampling gase may be adopted to accept more than one signal input. Uni-directional sampling gode with two imput Signale is shown below! D2 Control in Rut > The two inputs are Vs, and Vsz. -> The gare voltage has two levels; a higher level

which is usually zero and a lower level which

is regative

-> when the gente signal is at lower level the diodes are heavily reverse-Biasal and those is no conduction shoough them, the output voltage is zero. Hence, the negative level of the

## Advantages of Uni-disectional gate:

- i) It is very simple gauge.

- 2) The time delay is quite small, sine the input is coupled directly to the output through c, and diode.

- 3) The gave downs no worent in its quiescent condition.

- y) This gate can be easily extended into a multi-input or circuit with an ENHIBITOR or NOT terminal.

#### Disadvantages of Uni-dischional gate:

- i) There is underivable interaction between the input signal source and the gate voltage source.

- 2) The gare is of limited use because of the slow rise of the gare voltage at the diode.

control pulse may be considered as inhibitor signal.

Then the control signal is at its higher level (ie; ov) the diode get foreard brased (assuming the input signals to be positive pulses) and hance they conduct and the circuit is occapited as a capacitively coupled 2-input or grate with lower level of the gate signal as an inhibitor cignal.

Draw back:

As the number of inpute increases, the loading on the gate input increases heavily.

-> This difficulty can be solved by using additional diode as shown below.

sampling gave which avoids loading of gate signed

Here, the gate input voltage door not feed into the signal sources. Therefore by using above circuit it is possible to increase the number of input signals without encountering difficulties.

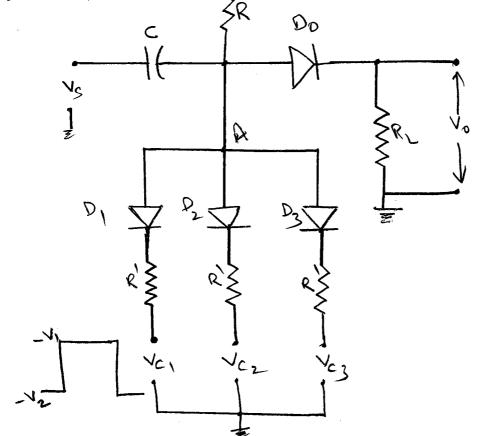

Sampling gate with multiple gate signals

The diode sampling gate with multiple gate signals is shown below!

In this the input signal is townsmitted to the output only whon all gate inputs are at their higher voltage levels.

- when all the gate signal inputs are at their higher voltage levels (-vi), the back blas on the diode Do is removed and the input signal is transmitted at the output.

- when any one of the gate signal ve is at lower level (-v2), the point A is negative with respect to the ground by an amount say v' and no past of the input wave-from is transmitted unless the input signal is larger than this walks the input signal is larger than this back-bias voltage (v') at point A.

-> This ciocuit is called of AND ciocuit.

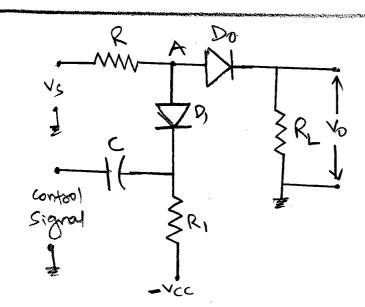

Sampling gate not sensitive to the upper level of the control voltage

In earliest circuits it is observed that, if

the highest level of the gate signal is not exactly

the highest level of the gate signal is not exactly

zero, either there is attenuation of the Imput

zero, either there is attenuation of the Imput

signal on the output signal gets superimposed

on a pedestal.

A gate whose sosponge is not sensitive to the upper level of the control voltage is shown below:

In the absence of the control signal, diode D, is forward brased and hance it conducts. The current through R developes a large voltage drop across it with the result that the wittage at A is less than the cut-in voltage of Do. Hence there is no conduction through Do and the output is zero.

→ If a positive going control signal is applied,

it is evident that the diode D, gets severlebiased and honce conduction through it stops.

biased and honce conduction and as a

Diode Do gets torward biased and as a

oresult the input signal gets transmitted

through the circuit too the duration of the

Control signal.

Too proper functioning of the gate, it is essential that the input signed is D.c Coupled (Resistor R), but the control signed may be either A.c. Coupled on D.c. Coupled.

Bi-disctional sampling gares

The Uni-Discotional gates have limitation that they townsmit signals of only one to lastity. They townsmit signals of only one to lastity. ie; either positive signals or regative signals.

-> Bilisectional gates can pass the signal of both the polarities.

Billisectional gares can be constaucted by using toansistous (or) Diodos.

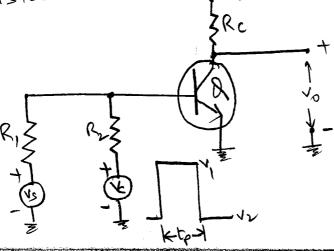

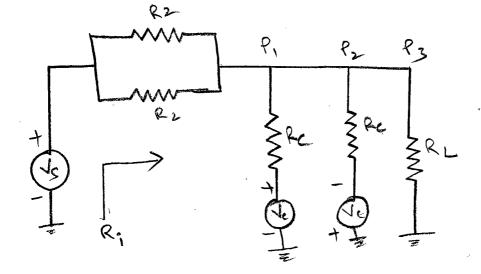

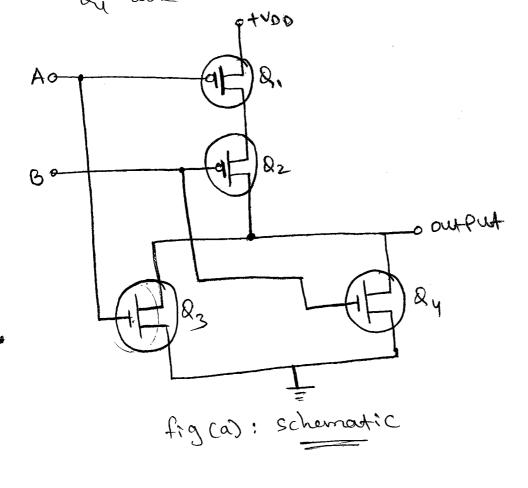

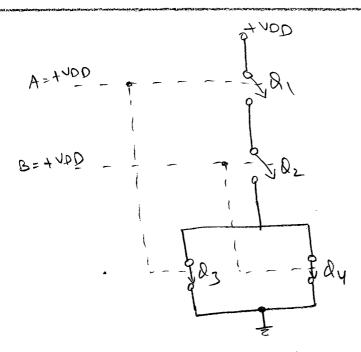

Bi-Discotional sampling gate using A linear bidiscational sampling gate using transistor is shown below:

RC

RC

- The signal voltage vs and the Control voltage vc are applied through the summing registors R, and R2 to the base of a transistor.

- The gare signal is a pulse waverfrom howing with a pulse width with a pulse width to equal to the sequired toaremission interval duration.

- when the getting signal vz is applied to the base of the toansistor of through seistor Re the toansistor well below Cut-off. It brosses the toansistor well below Cut-off. There there is no conduction and no transmission of input signal at the output.

- when the gate voltage is at its higher revery v, the toansistor is bragad above the cut-off to doine the toansistor in active off to doine the toansistor in active organ.

- Since the transistor is in the active region, the input signal is sampled for the region, the input signal is sampled for the duration of the gave pulse, and it appears duration of the gave pulse, and it appears in an amplified form at the output.

- Thus, this gate can handle the execussions of the input signal Vs in both positive and negative disections.

-> En the previous circuit both the input signal and the control signal are applied to a common base.

this circuit provider separate bases for the

The gate signal has two levels: a highest level  $V_2$ .

-> when the control voltage ve is at its upper level V1, Q, becomes on and the sculting emittee and the large and the voltage doop accoss it causes the potential of the emitted of 8,2 to rise such that & becomes cut-off. Hence those is no transmission of the input signal to the output. > when the control voltage is at its lower level V2, Q, is Cut-off and Q2 is food to operate of an amplifier. Thus it transmits the input signal in the amplified form of the output for the Subation of the gating signal.

#### Advantages;

During sampling interval(ie; transmission of the input signal transistor & is cut-off and hence there is no coupling between the input signal and the gating signal source. Input signal and the gating signal source. This reduces the looding effect on the signal source.

## Bi-Directional Diode sampling gate

A Bi-Directional sampling gate may be constorcted with the use of diodes instead of transistors.

Advantages of Diode gares

i) The linearity of operation.

2) Ease of adjustment to get zero pedantal.

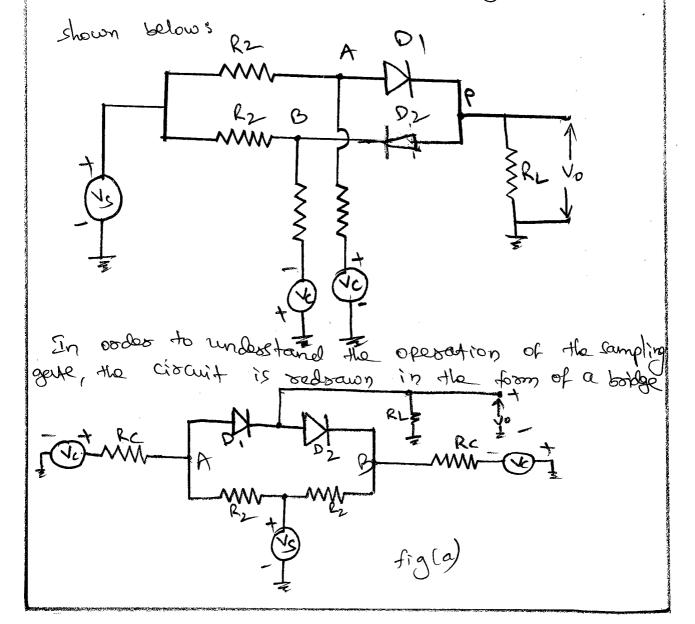

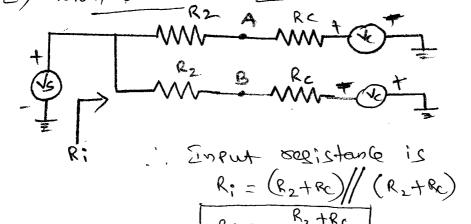

A Bi-directional two-diode sampling gate is.

> The circuit congists of two symmetrical gate signals the and -vo.

when the gare voltage levels are such that the voltage at Point A is negative (-Ve) and at point B is positive (+Ve) then both the diodes Dr and Dr as reverse biased and hence there is no toansmission of signals Vs.

when the gate voltages are such that the voltage at point A is positive (tvc) and the voltage at soint B is negative (-vc), then the voltage at soint B is negative (-vc), then both the diodos D, and D2 are ON. As a both the diodos D, and D2 are ON. As a sourt, there is a transmission of input rosult, there is a transmission of gate puller.

> It is impostant to note that the Diodep should be identical in characteristics to maintain the Complete Symmetry of the circuit so the complete Symmetry at the output that no pedestal can appear at the output in segponce to the gating voltages.

i) hain of the sampling gove

The gain of the sampling gate is defined as the source of vo during the toansmission interval."

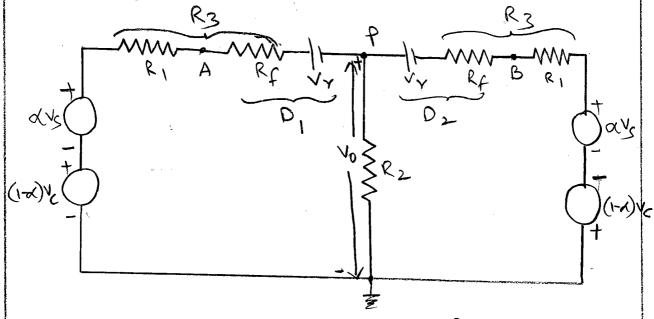

This can be easily calculated from the equivalent circuit desired from above figure by applying therenin's theorem at Point A and B and repaining the diodes with its piecewice linear model:

$R_f = fosward segistance of the diode.$   $V_r = C_{nt} - in voltage of the diode.$   $R_1 = R_2 || R_c = \frac{R_2 R_C}{R_2 + R_C}$

$R_3 = R_1 + R_f$  $\alpha = A+1enualion = \frac{R_1}{R_2} = \frac{R_c}{R_2 + R_c}$

$$V_{A} = V_{C} \times \frac{R_{2}}{R_{2}+R_{C}} + V_{S} \times \frac{R_{C}}{R_{2}+R_{C}}$$

but  $\frac{R_{C}}{R_{2}+R_{C}} = \alpha$ ,  $1-\alpha = 1 - \frac{R_{C}}{R_{2}+R_{C}}$

$$= \frac{R_{2}+R_{C}-R_{C}}{R_{2}+R_{C}} = \frac{R_{2}}{R_{2}+R_{C}}$$

$$V_A = V_c (1-\alpha) + V_c \alpha$$

. From the equivalent circuit of above fig, we observe that the effect voltage (Vr) and gate woltage components (1-x)Vc] sends equal currents in opposite directions through Ri.

Hence the net Current R, Que to them is Zero. Therefore open circuit voltage at point P with seprent to ground is  $\alpha V_s$ .

Therenin's agrivalent citait between the point p' and ground is shown below:

The open croant voltage from P to ground is  $Q^{\nu}_{s}$  and therenin's registance is  $\frac{R_3}{2}$ .

The output voltage

$$V_0 = \alpha V_S \times \frac{RL}{R_L + \frac{R_3}{2}}$$

but  $\alpha = \frac{Rc}{R_2 + Rc}$

$$V_0 = \left(\frac{R_C}{R_2 + R_C}\right) V_S \left(\frac{R_L}{R_2 + \frac{R_2}{2}}\right)$$

in hain

$$(A) = \frac{V_0}{V_S} = \frac{R_C}{R_2 + R_C} \left[ \frac{R_L}{R_L + \frac{R_S}{2}} \right]$$

i) hate Control voltage Vc:

for proper operation of the sampling gate it is necessary to conduct both the diodep over the recessary to conduct both the diodep over the full range of the ingut signal and both diodep should be back biased when no sampling takes place.

These contesia's impose two restoictions on the control voltage levels:

- i) minimum positive control voltage level (Vc) min

2) Znitially in the presence of only gate voltages

Diodes D, and D2 Gubent conduct equal cubsents

there the load curseant is zero and the

Pedestal is zero.

- 3) Assume, that  $V_S$  is a positive going signal, then the awarent in D, incoases and the authorized in D2 decreases, hence the difference awarent flows through RL. As  $V_S$  continues to incoease eventually, the awarent in D2 becomes zero i.e. D2 will be aut-off.

apetermination of minimum positive control voltage level (Volmin:

- To maintain conduction of D2, these is a restriction on the minimum value of the restriction on the minimum value of the Positive level of Control voltage, when signal voltage attains a marximum voltage vs.

- To Complete the required minimum positive voltage (Vc) min, assume that diade D2 has unltage (Vc) min, assume that diade D2 has been some agrivalant

Cident, the voltage across

$$R_3$$

associated with in  $P_2$  is zero and neglecting  $V_1$  i.e.,  $V_2 = 0$ , the output voltage is given by

$V_0 = \alpha V_5 - (1-\alpha) V_6 - - Considering orginal sight since  $R_3$  across  $P_1 = 2exo$

$V_0 = (\alpha V_5 + (1-\alpha) V_6) \frac{R_L}{R_L + R_3} - Considering 1 Reft 100P$

equating two equactions for  $V_0$

$(\alpha V_5 + (1-\alpha) V_6) \frac{R_L}{R_L + R_3} = \alpha V_5 - (1-\alpha) V_6$

$(\alpha V_5 + (1-\alpha) V_6) \frac{R_L}{R_L + R_3} = \alpha V_5 - (1-\alpha) V_6$

$(\alpha V_5 + (1-\alpha) V_6) \frac{R_L}{R_L + R_3} = \alpha V_5 - (1-\alpha) V_6$

$(\alpha V_5 + (1-\alpha) V_6) \frac{R_L}{R_L + R_3} = \alpha V_5 \left[1 - \frac{R_L}{R_L + R_3}\right]$

$(1-\alpha) V_6 \left[\frac{R_L}{R_L + R_3} + \frac{1}{R_1}\right] = \alpha V_5 \left[1 - \frac{R_L}{R_L + R_3}\right]$

$(1-\alpha) V_6 \left[\frac{R_L}{R_L + R_3} + \frac{1}{R_2}\right] = \alpha V_5 \left[\frac{R_L}{R_2 + R_3}\right]$

$(1-\alpha) V_6 \left[\frac{R_L}{R_1 + R_2} + \frac{1}{R_2}\right] = \alpha V_5 \left[\frac{R_L}{R_2 + R_3}\right]$

Substitute  $\alpha = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_1 + R_3}\right] = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_2 + R_3}\right] = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_2 + R_3}\right] = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_2 + R_3}\right] = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_2 + R_3}\right] = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_2 + R_3}\right] = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_2 + R_3}\right] = \frac{R_C}{R_2 + R_6}$

$\left[1 - \frac{R_C}{R_2 + R_3}\right] V_6 \left[\frac{2R_L}{R_2 + R_3}\right] = \frac{R_C}{R_2 + R_6}$$

$$V_{C} = \frac{R_{C}}{R_{2}} \cdot \frac{R_{3}}{2R_{L}+R_{3}} V_{S} = (V_{C})_{min}$$

Sthis is the minimum positive value of the Sthis is the minimum positive value of the Control voltage required to ensure signal transmission over the full range of the input signal by keeping both the Diodes Conducting.

-> from the above equation, (Vc)min Decreased with incolaring RL.

(Vc)min  $\propto \frac{1}{RL}$

However we cannot increase R\_ beyond Gestaly limit, because increase in R\_ increase R\_C time constant where C= strong capacitance across the cuput terminals.

As RLC incorposes, most time is sequised to desay output voltage to test value when the diode cut-off of the end of the gating signal.

Desermination of minimum negative control voltage level (Van) min:

-> During no sampling period both the Goder should be back-biased. But it negative control vo Hage is not sufficient enough then at the maximum voltage of the input signal diode D, may be forward based.

-> 50, to eneuer that both Dialog are back-biased (off) when no sampling is to take place those should be minimum negative value of the control

-> when both the diodes are reverse-biased, point P in agrinalent cioauit is at ground

potential.

· voltage across D, is x vs - (1-x) vc

50, for D, to be severe brased this voltage must be either negative on in worst call

· ~ Vs - (1-x) Vc =0 d Vs = (1-x) Vc  $V_c = \frac{\alpha V_S}{1-\alpha}$

sub

$$\alpha = \frac{Rc}{R_2 + Rc}$$

$$V_c = \frac{Rc}{R_2 + Rc}$$

$$V_c = \frac{V_s Rc}{R_2 + Rc}$$

$$V_c = \frac{R_c}{R_2 + Rc}$$

$$V_c = \frac{R_c}{R_2 + Rc}$$

$$V_c = \frac{R_c}{R_2} V_s = (V_{cn})_{min}$$

This is the minimum regative value of the control voltage organised to existe back-biased (off) of the Diode during no sampling period.

In poactice, larger values of (Vcp)min and (Vcn)min are choosen.

A larger value of (Vcp)min improves linearity in addition to safety.

"ile) Signal in Put Registance (R:);

51. Assume Ideal dioder le; RF=0, Ro=0, V=0

I) when diodog are conducting:

i suput registario is

$$R_{i} = \frac{R_{c}}{2} / R_{L} + \frac{R_{2}}{2}$$

$$R_{i} = \frac{R_{c}R_{L}}{R_{c} + 2R_{L}} + \frac{R_{2}}{2}$$

$$R_{i} = \frac{R_{c}R_{L}}{R_{c}+2R_{L}} + \frac{R_{2}}{2}$$

(1) When diodes aros not conducting:

Problem: In a bidirectional diode sampling gate, assume that R\_= Rc = 100 ks, R2 = 50 ks and that the signal how a peak value of 200. Find. a) Gain A, b) (Vcp)min c) (Vcn)min d) R; and e) 3-dB foregreency of the gase. (Assume total Shunding Capacitance of 20PF) SOI: Assume Diodos are perfect and ideal a) Gain (A) =  $\left[\frac{R_L}{R_L + R_3}\right] = 0.57$ b) (Vcp) min = Rc (R3 / Vs = 5.7V g) (vcn)min = Rc x Vs = 40V d)  $R_i = \frac{R_c + R_L}{R_c + 2R_L} + \frac{R_2}{2} = 58 \text{ kg} \text{ (when Godog ask)}$  $R_i = \frac{R_2 + R_C}{2} = 75 k \cdot R_c \text{ (when Diodeg assembly)}$ e) 3-dB foregrency (fz) = 1 when T=RC  $n = \frac{R_1 R_L}{R_1 + 2R_1} \left( C_0 + 2C_C \right)$ 1=0.29MS  $f_2 = \frac{1}{257 \times 0.29 \times 10^6}$ £ = 0.55 MHZ

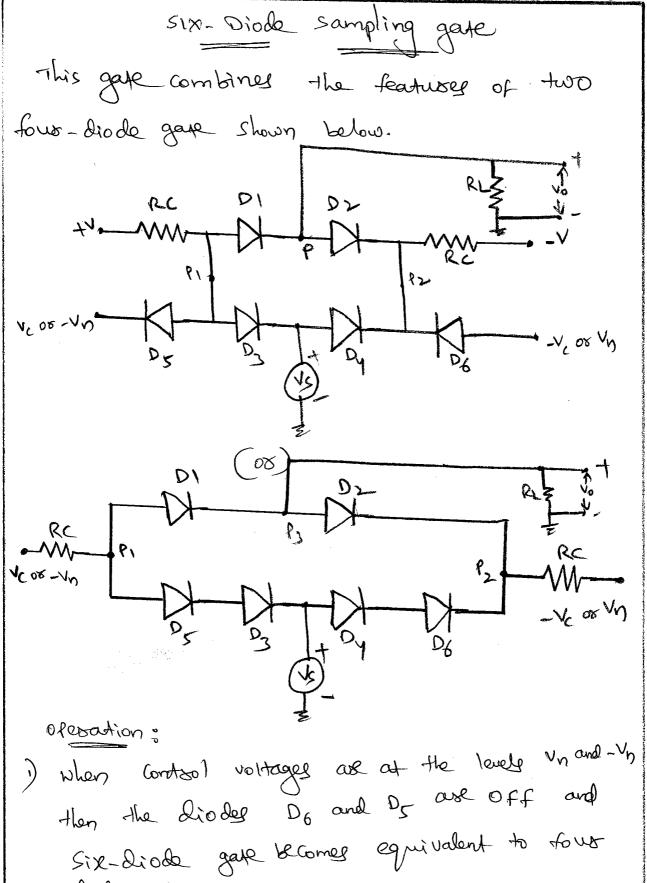

#### operation:

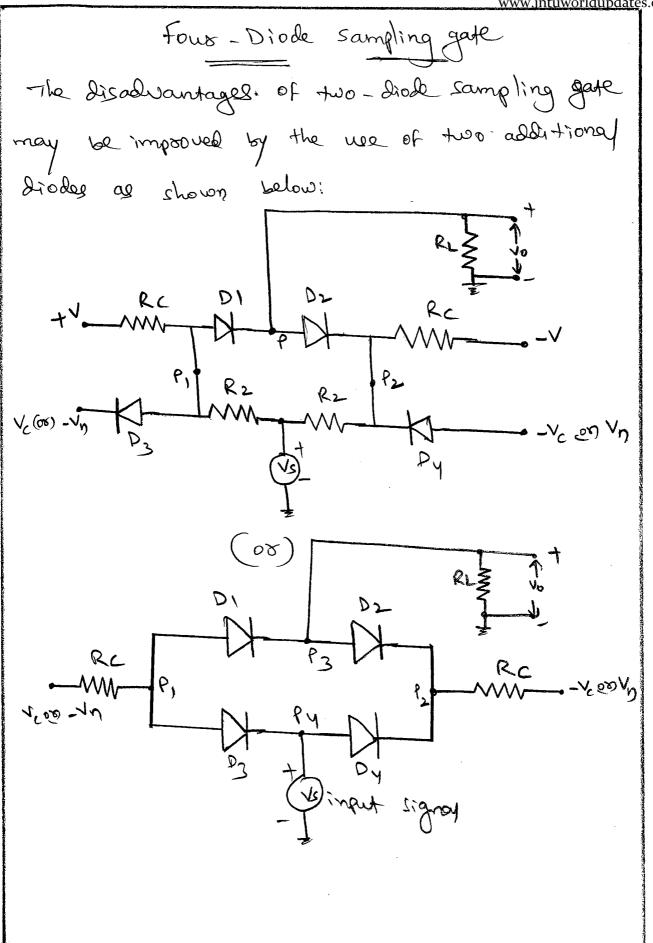

- i) when the control voltages are at levely ve and -ve All four Diodos are forward brased and so the input signal is connected through two diodos parallel paths each consisting of two diodos in series. So, signal transmission takes place.

- 2) when control voltages are at levels in and in all four diodes are off, so no signal transmission takes place

\_'. Vo = 0.

- The required voltages ve and -ve depend on the amplitude of the signal vs and over the amplitude by the condition that the current determined by the condition in each of the diodes be in the forward direction in each of the diodes D1, D2, D3 and D4.

- -> The awarent in each diade consists of two Components:

- ) Due to ve as shown below Ag (a).

- 2) Due to Vs og shown below fig (b).

is equal to  $\frac{V_S}{R_C} + \frac{V_S}{2R_I}$ . This currount must be

1885 than  $\frac{V_c}{2R_c}$  (which is due to  $V_c$  through  $D_3$ ) so that  $D_3$  conducts.

$$\frac{v_c}{2R_c} = \frac{\left(\frac{v_s}{R_c} + \frac{v_s}{2R_L}\right)}{\frac{v_c}{R_c} + \frac{v_s}{2R_L}}$$

$$\frac{Vc}{2Rc} > Vs \left[ \frac{1}{Rc} + \frac{1}{2RL} \right]$$

$$\frac{V_{C}}{2R_{C}} > V_{S} \left[ \frac{2R_{L} + R_{C}}{2R_{C}R_{L}} \right]$$

$$V_{C} > V_{S} \left(2 + \frac{R_{C}}{R_{L}}\right)$$

i minimum value of Vic required to keep.

P3 ON is

Hence it is alcumed that Rf << R 08 RL.

The Rf and R are < Rc and RL, gain will be very close to when the control voltages are Vn and -Vn they

all the Godge as severe braced.

If the signal has a peak amplitude is, then

the minimum voltage organised at P2 to keep Dy

off is (Yn)min = Ys

Assume

$$V_S = 20V$$

,  $R_f = 25.7$ ,  $R_L = R_c = 100K$ . And  $R = 100$  s. Find A,  $(V_C)_{min}$  and  $(V_D)_{min}$  for four-diode gate?

$$sol : A)(V_c)_{min} = V_s \left[2 + \frac{Rc}{RL}\right]$$

$$= 20[2+1] = 20\times3$$

$(Vc)_{min} = 60 V$

(so)

(50):

$$\alpha$$

$A = \frac{RC}{RC+R_2}, \frac{RL}{R_L+(\frac{R_2}{2})}$

$$A = \frac{100 \text{ kg}}{100 \text{ kg}} \times \frac{100 \text{ kg}}{100 \text{ kg}} + \frac{2.01 \text{ kg}}{2} = 0.97$$

$$V_{cp} = \frac{R_{c}}{R_{2}} \left( \frac{R_{3}}{R_{3} + 2R_{1}} \right) \cdot V_{s}$$

$$= \frac{100 \text{ kg}}{2 \text{ kg}} \left( \frac{2.01 \text{ kg}}{2.01 \text{ kg}} + 2 \times 100 \text{ kg} \right) \times 25$$

$$= \frac{100 \text{ kg}}{2 \text{ kg}} \times \frac{2.01 \text{ kg}}{2.01 \text{ kg}} \times 25$$

$$= \frac{100 \text{ kg}}{2 \text{ kg}} \times 25$$

dide gave

2) when the control signals are at levely Vc and -Vc Drodge D6 and D5 Conduct and the points 12 and 1, are damped to those levels. Hence D3 and Dy out back biased and

Signal toansmission takes place.  $V_{min} = V_{S} \left( 2 + \frac{RC}{RL} \right)$

-> (Vc) min for four diode gate en Vmin for 6-diode get may be as large as 168.757 for 25V signal.

Advantage:

Advantage of six-diode gate is that such a large voltage vmin needed appear only as a fixed voltage but not as a control signal as in Low- Diode gate.

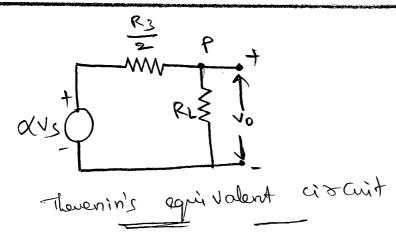

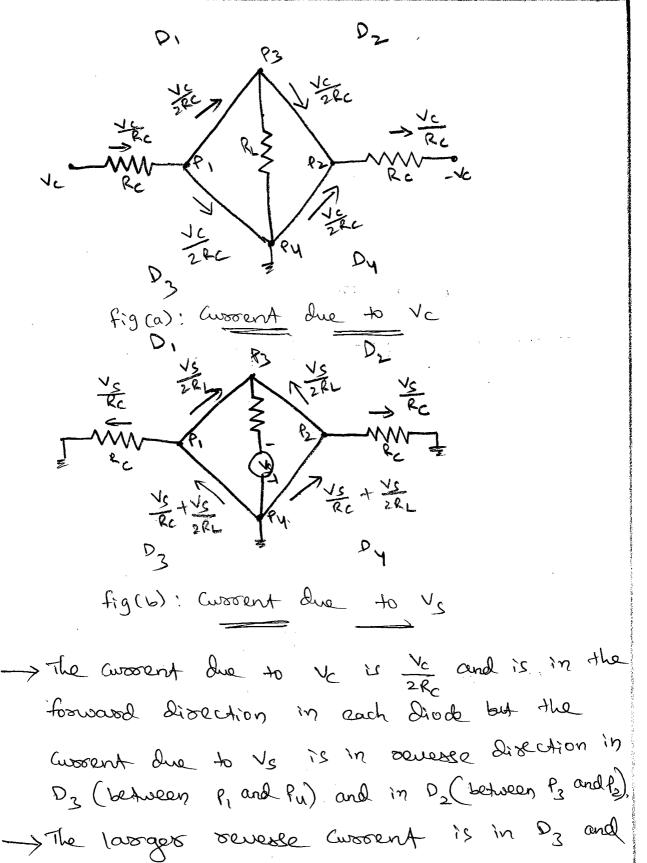

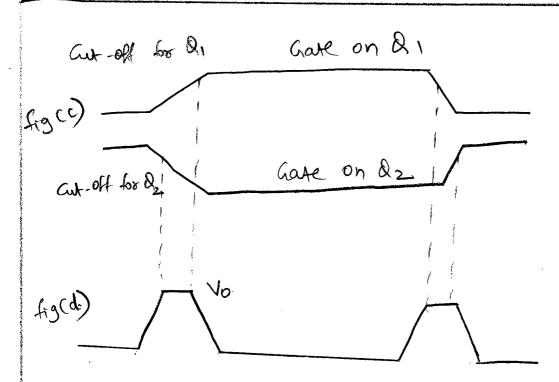

Reduction of pedestal in a Gaze Go Cuit -> In Bi-Directional toangistor sampling circuit if no gating signal is applied the voltage level at the output is vcc. -> when the gating signal is applied, the transistor downs awarent and the output there fore cetablisher itself at a new lower quiez cent level. -> Now, when the signal is applied, the output signal is superimposed on this new quiescent The appearance of the output during a gesting interval is shown below, where the sampled POSTION of the signal is supposingosed on a pedestal. Sampled output, %

fig (a)

-> The Pedestal can be largely supposessed by the Symmetrical arrangement shown below: -VBB1 b) A linear gate circuit with provision to concel the pedestal. > Ein this, the gotting and signal voltage have been placed directly in sexing. > A Pair of transistors is used and the bases of transistors are driven by the gating signal of opposite polasity.

d, = Gating transis too. R2= It is used to minimize the pedeptal.

- During the toans mission time to i.e., when the control signal is at its upper level Q, conducts and Q2 is cut-off. A current flows from Vcc through Rc and Q1.

- During no sampling time (non-transmission time) when the control signal is at its lower level,  $R_1$  is off and  $R_2$  conducts and a current flows from vcc through  $R_c$  and  $R_2$ .

The biog voltages - VBB, and - VBB2 and the gate signal amplitudes are adjusted so that the two transits too arrownts are that the two transits too arrownts are identical. As a result the quiescent output identical. As a result the quiescent.

The gave voltage has finite vice time the then the voltage spikes appear in the objectionable output. These spikes may not be objectionable if the gave voweform vise time is small if the gave voweform vise time is small in comparison with the gave duration.

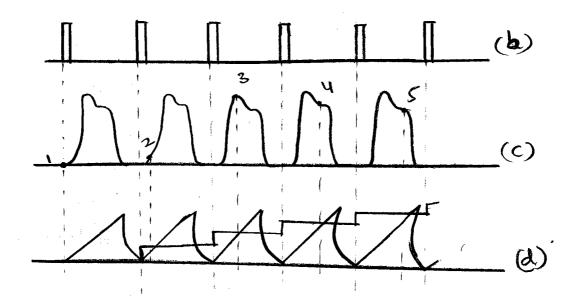

fig(c): Gating wavefrom of fig(b) doown with non-zero rise time

fig(d): Spikes which may occur in the output ciocuit of fig (b) due to goting wowe form with non-zero rise time.

Doarbacks of fig (b):

- i) It the gotting wave from have definite sill and fall times two sharp spikes are generated at the output.

- 2) There is a continuous flow of aversent through Rc and So it has to dissipate a lot of heat.

- 3) the circuit is complicated, since it sequises two bias voltages i.e. -VBB, & -VBB2 and two constons Signal sources which are complements of each other.

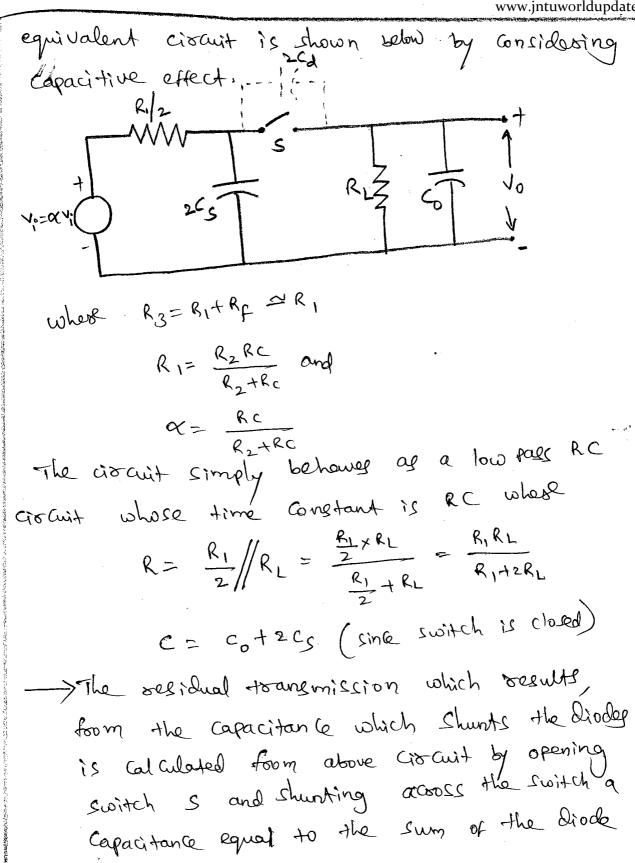

# Effect of circuit Capacitance on bidirectional Gode

The capacitances which effect the operation of gate circuit how the following:

- 1) Capacitance Co across the bidirectional Sampling gate output terminals.

- 2) Capacitane of across each diode.

- 3) Stoay CapacitonCer Cs from each of the junctions of the registors R2 and Rc to ground.

- -> The capacitone Co, has an adverse effect on the ability of the sampling gate to toansmit fact waveforms due to finite sise time and fall

- -> The capacitance cs, not only affects the ability to transmit fast wave forms but also limits the speeds with which the gate can be opened and

closed.

- >The diode capacitance Cd, provides a transmission Roth through the gate even when the diodeg are not Conducting.

- -> Assuming Rf=0, R8=00 and ideal diode, when the diodes are forward biased, the

Capaci tances.

### Disadvantages of two-libde gate:

- i) hain is low.

- 2) sensitive to control voltage imbalance.

- 3) There may be appreciable reakage through the lide Capacitance.

- y) There is a possibility that (Vn)min may be excessive.

Applications of sampling gate

) chopper Amplifier

- -> One of the application of a sampling gate is chopper amplifier.

- → Need:

suppose a small signal (of the order of millivolts), v(t) having very small  $\frac{dv}{dt}$  is

be amplified using

·) Ac amplifier: coupling capacitors between

stages would not be feasible, since these coupling

Capacitances would be

impoactically large.

2) DC amplifier: it is not possible to Distinguish between a change in output voltage as the result of a change in

input voltage on as the result of a doiff in some active device es component. In this case a chopper amplifier can be used. chopper stabilized complifies is shown below fig(a). AC Amplifich fig (a): A chopper stabilized Amplified Ó fig(b): Input signa fig (c): chopped fig(d): signalmadulared sparkThe low-forguency input signal v(t) is shown in fig(b).

Assume that switch s, is being doiven so that it is alternately open and closed. Then the signal vi(t) at the amplifies in put will appear as shown in fig (c).

i.e. when  $S_1 = open$ ,  $V_1(E) = V(E)$ when  $S_1 = closed$ ,  $V_2(E) = 0$

so, the signal vill) is a "chorpped" vession of

v(t).

The ciocust Congisting of R and S, is

called chepper.

signal vict) reproduces the input signal vit). so, signal vict) reproduces the input signal vit). so, a perceptible voltage change takes place in vit) a perceptible voltage change takes place in vit) about when si is open. Thus, when during any interval when si is open. Thus, when vit) is positive, the positive extremitive of the value form vitt) are not at a constant voltage and wave form vitt) are not at a constant voltage and similarly for the negative extremitive when vit) similarly for the negative extremitive when vit) is negative. But this feature is in no way essential

to the operation.

If the foregrency of operation of the switch is very large (typically 100 times) in Comparison with the foregrency of signal V(t). Therefore no appreciable change takes place in V(t) during the interval when S, is open.

so, Vo(t) may be considered as a squareusave of amplitude proportional to VIE) and

howing an average value (shown dashed in fig c)

thouring an average value (shown dashed in fig c)

that is also proportional to the signal V(t).

That is also proportional to the signal v(t).

Alternatively the signal ViII) is a square wave

at the switching foregreency, amplitude-modulated

at the switching foregreency, amplitude-modulated

by the input signal and superimposed on a

signal which is proportional to the input signal

v(t) itself.

Thus Volt) is applied to an amplifier, if

this framplified is designed to act as a

this framplified is designed to act as a

filter to eliminate the signal itself i.e.

average value from volt, then the chopper

average value from volt, then to eliminate

(or chopper together with a filter to eliminate

the signal itself) is called a modulator?!

The output of this modulator is a modulated by as shown in fig (d). modulated by adjusting the low-forgardy this is obtained by adjusting the low-forgardy cut-off of Ac amplified in Such a way

that oblatively high foreguency square wave passes with small distortion while the signal foreguency is well below the Cut-off point so that it is rejected.

only the modulated wave from as shown in fig (d) A will appear.

High forequency

Signal lower aut-off

forequency

Forquency

The original signal is recovered through the mechanism of the capacitor c' and switch s<sub>2</sub>.

Let the switch so closed and opens in synchronism with so. Thus during the interval interval to the regative entremity of VALE) interval is restored to zero and during the interval is restored to zero and during the interval is reduced to zero. To, the positive entremity is reduced to zero.

Except for an increase in amplitude.

The signal voltacross S2 is same as the signal vill.

-> If this signal volt) is passed through a low-pass filter, it rejects the square wave (high frequency) and transmits the signal frequency.

-> At the filter output, amplified replica of the original signal is obtained.

> If so operated antisynchoronously with S, (so closed while s, is open and vice-verse) s, (so closed while s, is open and viil appear than at the output the signal will appear with reversed polovoity.

-> In either case, the combination of the capacitor c, switch so and the filter is called "synchronous demodulator."

Note:

The simplifies is not stabilized by the choppers eliminate choppers but outher the choppers eliminate the press eliminate the press but outher a lisect - coupled stabilized the necessity for a lisect - coupled stabilized amplifier.

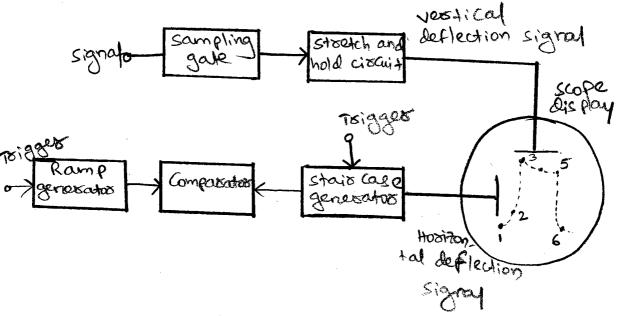

# 2) Sampling Scope

-> An important application of a sampling gate is in sampling scopes.

> Basic principle of sampling scope:

In this scope, the Display consists of a sequence of samples of the input wave form each sample taken at a time progressively delayed with rospect to some reference point in the come form.

fig (a) shows the block diagram of a

sampling scope;

fig (a): Block diagram of sampling - Sco Pe

- b) Toiggesing signal

- c) signal to be observed

- d) The samp and stair call signals

- > Assume that the waveform to be Displayed. is a pulse in the toain of pulses as

- shown in fig(c).

- -> fig (b) separants a toain of toiggers whose time of occurrence proceeding somewhat the pulsop, These toiggets are used to toigget speep and a start step signal.

#### operation:

- -> The stair-step and round signale are applied to a comparator.

- The stair-step source as the reference voltage and in each cycle, whenever the ramp afterns the stair-step level, the Comparator afterns the stair-step level, the comparator produces a pulse output which is used as the control signal of the sampling gate.

- -> At each such control signal, the gate

produces its output a sample of the

- -> The eample having a duration equal to the width of the Control pulse.

- that during its interval no sensible change

- takes place in the input signal.

Thus the gase output, at each control

- Signal, is a voltage equal to the signal voltage at the time of sampling.

- The Points at which samples are taken

have been masked by dots 1,2,... as shown in fig (c).

>2+ is seen that the samples are taken at a time, which is progressively delayed by equal incoments.

-> The sample consist of a pulse whose duration is equal to the duration of the sampling gate Control signal and whose amplitude determined by the magnitude of the input signal at the sampling time.

-> This voltage must be hold till the next Sample is taken. This holding operation may be obtained by applying the gate output to charge a capacitor through a drode to the . peak value of the sample so that when the sample is completed, the capacitor holds its

-> But the sample is so short in Duradion that

it is not possible to charge a capacitor

in this small interval.

-> Therefore, before the sample is applied to the "hold", diode- Capacitos Combination, it is first passed through an amplition stage whose

output time constant is large.

- -> The sample pulse is theorety widered ie; "stoetched" and now will have a much booader peak.

- It is stocatching and holding operations are performed by the block so labelled in fig (a) performed by the block so labelled in fig (a) be for the sample is applied as a westical. Defore the sample is applied as a westical. Defore deflection signal to the scope. And before each new sample is to be taken, the hold each new sample is to be taken, the hold capacitor must be discharged.

- The stair-step signal generator produces the scope.

Thorizontal-deflection signal for the scope.

Thus the CRT spot moves horizontally across the score in jumps and at each new the scoren in jumps and at each septically by Rosition, the spot is deflected vertically by an amount proportional to the sample height.

- The CRT beam is moomally blanked and is un-blanked only at the time of the display of the sample.

- -> CRT screen Consists of a series of John of the original signal signal signal signal as shown in fig (a).

www.jntuworldupda

The sampling poinciple finds application in a

scope used to display very fast periodic

same forms i.e., wave forms with rise times in

the nanosecond range.

## Logic families

Realization of Logic Gates using Diodes & Toansistook

) Diode AND hate: AND hate is also called as coincidence out.

> An AND gate how two (00) more inputs and a single output.

The output of an AND hate is 1 if and only if all the inputs assume 1 state."

The IEEE standard for AND circuit is given in fig (a) together with the Booken expression for this gove.

| A | A | -1 |

|---|---|----|

|   |   | •  |

Y= AB-. N fig (a): 2 €€ Standard

| Inp | w | output |

|-----|---|--------|

| A   | B | 1      |

| 0   | 0 | 0      |

| 0   | 1 |        |

| 1   | 0 | 0      |

| 1   | 1 | •      |

fig (b): Touth table

a) Diode AND hate for positive logic

V(1) A a MM H

output y

Assume R>>Rs so that droop across Rs con be neglected.

let V(1) = 4014age corresponding to logic 1 = + Vcc = +54

VR = Reference voltage

Rs = Source Registance

1 = output of gate

D, D2 = 2 dentical diodes

A, B = logic in puts R = Pull ul Registor

Resistor R is called Pull-up resistor because in some sense it Pulls the output from logic low to logic high.

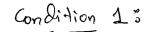

condition 1:

Let A = B = V(1) V(1) V(1) V(2) V(3) V(3) V(3) V(3) V(4) V(5) V(5) V(7) V

Both dioles are Roverse biased and represents open circuit. Since there is no path for awant flow through resistor, it will not have any drop across through resistor, it will not have any

it and VR=VCI) appears at the output.

in when A = B = V(1), output Y = V(1).

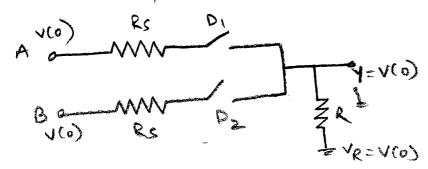

condition 2:

Diode D2 conducts and Diode D, semains off.

since current flows through R, Diode D2 towards

v(o) (ground) and we get drop across Diode D2 at

outent

ideally

$$Y = 0$$

proactically  $Y = 0.7V$

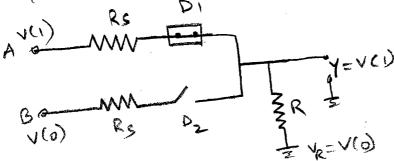

Condition 3:

when

$$A = V(0)$$

and  $B = V(1)$   $V_R = V(1)$

A  $V(0)$

A  $V(0)$

B  $V(1)$

R  $V(1)$

P, conducts and Pz goes off and output again becomes the Doop across Diode

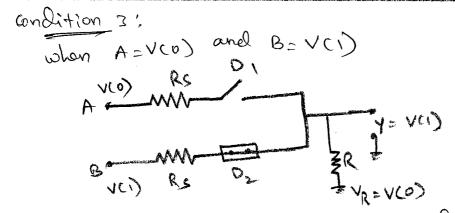

Condition u:

Both lides P, and P, conducts howing a droop of 0.74. Again this doup appears at output.

| Practically | Y = | 0.77 |

|-------------|-----|------|

|-------------|-----|------|

| Snputs    | 01   | MPM         |

|-----------|------|-------------|

| A B       | 1    | 109ic state |

| 1(0) N(0) | 0.7V | LOW         |

| v(0) v(1) | 0.77 | Low         |

| V(1) V(0) | 0.77 | Low         |

| 4(1) 4(1) | vci) | High        |

6) D'ode AND gare for negative logic: PI

In this V(0) = high tow high tow +5V

so, it any imput is at a level v(0), The diode. Connected to this input conducts and the output is clamped at the voltage vco)

Et all imputs ask at I level VCI) then all diodox are reverse-biased and No=VCI)

The AND operation has been implemented.

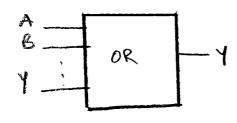

- 2) Diode or hate:

- -> It has two coss most inputs and a single output.

- $\rightarrow$  "The output of an or gate is 1 if one extended inputs ask 1".

- -> The IEEE standard symbol for or circuit is shown in below fig (a) together with the Boolean expression.

Y=A+B+...+N

fig(a): Effe standard for or gate

| Inp | ut | MANG |

|-----|----|------|

| A   | B  | 7    |

| 0   | 0  | 0    |

| 0   | ١  | ţ    |

| 1   | O  | þ    |

| L.  | 1  | 1    |

fig (b): touth table

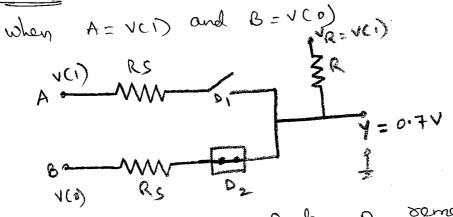

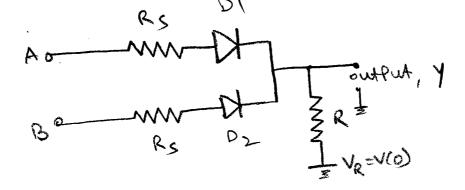

a) Diode or gate for positive logic:

Both the diodes D, and D2 as severe biased so no Current flows through R and output is Y = VR=VCO) = LOW

condition 2:

diale D, conducts and D2 remains off, thus a Current flows through resistor R starting from

input A through Di, R to ground.

$$y = v(1) - v_r = v(1) - 0.7 = high.$$

diode D, is reverse biased and diode D2 is

froward biased

condition y:

when

$$A = V(1)$$

,  $B = V(2)$

RS D1

RS D2

REV(1)

RS D2

REV(1)

Both diodog &D, & D, are forward brased ... y= v(1)-V\_ = high

| Let VCI)=SV  | 20   | PWS  | 00   | HPWS       |

|--------------|------|------|------|------------|

| : Y= V(1)-V+ | A    | B    | Y    | 108ic 5+ak |

| =5-0.7       | V(0) | V(0) | v(6) | Low        |

| 4=4.3V       | u(o) | 161) | 4.3  | High       |

| ι , -        | 400  | N(o) | 4·3V | High       |

|              | 10)  | 4(1) | 4.34 | High       |

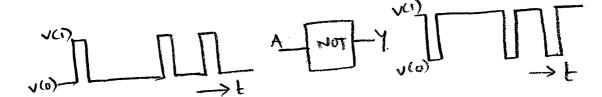

3) NOT gate:

-> It is also called as Invester circuit.

-> It has single input and single output

-> The output of a NOT CIOCUIT is 1 if and

if the input is a and vice vessa".

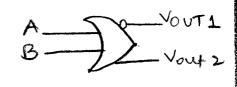

-> The IEEE standard with negation at the input of a logic block is shown in fig (a) and negation at the output of a logic block is shown in fig (b) along with the touth table in fig(c)

| <i>".</i> | <b></b> |

|-----------|---------|

| Ao        | Y=Ā     |

| Input | output |

|-------|--------|

| A     | Y      |

| 0     | ١      |

| l     | D      |

fig(a): Negation at input b) Negation at output

c) soot routh table

Equation is Y = A en A'

-> since it inverts the sanse of the output with segget to the input, it is also called as invested.

-> The toansistor gravit below shows an invested for Positive logic: o state of v(o)= VEE 1 state of VCI) = VCC (06) VEE = V(0) fig@): An invester for positive logic A similar circuit using P-n-p transistor is used for a regative-logic Not Circuit. ·) It the input is low, v=v(0), then the parameters

over chosen so that Q is off

, 10 = 100 = 101).

ii) If the input is high, V=V(1), then the circuit Parameters are chosen so that & is in Saturation

, 10=1= 10)

Fig) If the silicon toansistor in bolow fig has a minimum value of hff of 30, find the output levels of 0 and 12V?

gol: Given data

$$hf \in = 30$$

$$Vcc = 12V$$

$$Vee = -12V$$

$$R_1 = 15 K R$$

$$R_2 = 100 K R$$

$$R_C = 2.2 K R$$

Since

$$V_B = -1.56 V$$

Since  $V_B$  is regardine,  $Q$  is  $Cut-off$

$V_0 = 12V for V_0^* = 0$

let up versify the assumption the Q is in

saturation.

Assume transistor saturation parameters are person

$$Z_{BCmin} = \frac{R_{C}}{n_{fe}}$$

from fig,

$$\Sigma_1 = \frac{V_1^*}{R_1} = \frac{12}{15} = 0.80 \text{ mA} = \frac{V_1 - V_B}{R_1} = \frac{V_1^*}{R_1}, v_B = 0$$

$$Z_2 = \frac{V_1'}{R_2} = \frac{12}{100} = 0.12 \text{ mA} = \frac{V_8 - (-V_{EE})}{R_2} = \frac{0 - (-12)}{R_2}$$

doop across transistor is terro

and the Go Cuit has per formed NOT operation,

let us assume toansistoo junction voltages

for sili Con toansistor, VBECOUT) = 0.7V, VCECSOUT) = 0.3V

$$Z_{c} = \frac{V_{cc} - V_{c} \in Cat}{R_{c}} = \frac{12 - 0.3}{2.2} = 5.31 \text{ mA}$$

$$I_1 = \frac{V_{in} - V_{BE}(act)}{R_1} = \frac{12 - 0.7}{15K} = 0.75mA$$

since 28 > 28 (min) so, & is in saturation 50, if v = v(0), V=12V 1:= V(1) , V0 = 0.3V

classification of Logic families:

- 1) Bipolas Logic families

- a) Direct-Coupled transistor logic (DCTL)

- b) Rosistor-Transistor logic (RTL)

- c) Resistance capacitonce toansistos logic (RCTZ)

- (170) sign tooksismost aboid (bTL)

- e) Joansistor-reansistor logic (7772)

- f) Cursonent mode logic (CML) 000 ECTL

- 2) Mos logic families

- a) NMOS

- b) PMOS

- c) cMOS

"Logic family is defined as a group of compatible Icle

with the same logic levels and supply voltages which

parform various logic functions and last fabricated as

per a specific circuit configuration."

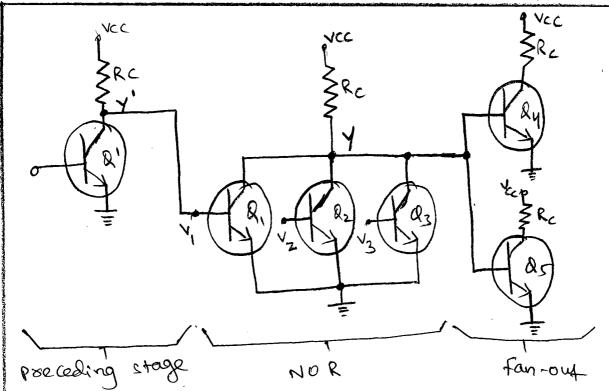

) ROSISTOS - TOURSIZONS logic (RTL); -> The Basic RTL gate is NOR gate -> RTL cio Cuit consist of resistors of Toansistors fig (a) below shows 2-input RTL NOR gate RB fig (a): 2-input RTL NOR gate Emitters of both the transistors are connected to a Common ground and Collectors of both toansistors are tied together through a Common Collector registor Rc to a supply voltage Vcc. The registor Rc is known as passive Pull-up २०६९,८४०. operation: > Enputs representing logic levels are applied at A and B terminals.

-> In RTL gave, the input voltage Googponding

to Low level is seguised to be low enough

for the corresponding transistor to be Cut-off. -> similarly, the input voltage coords ponding to HIGH level should be high enough to doive the Cossesponding to ansistor to saturation.

Condition 1:

when both the inputs are high.

i-e; A = V(1), B = V(1)

Both transistors & and Q2 goes to ON state (saturation) and the voltage at Collectors is

NCE sat.

1. Y = VCE(sat) = 0.2V = LOW

Condition 2 ;

when both the inputs are 100

ic; A= V(0), B= V(0)

Both toansistors &, and Q2 goes to off State (Cut-Off). Thus no current flow through Rc and doop across Rc is zero. so, complete vec is

will appears at output

condition 3 %

when only one input good high i.e., when A=V(1) and B=V(0) (08) A=V(0) and B=V(1)

The toansis too feeded with high input conducts causing a curorent to flow through on toansis too and the toansistoo enters into on toansis too and the toansistoo enters vector) eatworking. Thus the output voltage becomes vector)

1. In both the Conditions 1 = VCECCOAT) = LOW

| Inp  | wt s | outents  |             |  |

|------|------|----------|-------------|--|

| A    | B    | Y        | logic state |  |

| 1(0) | 1(0) | VCC      | High        |  |

| J(0) | 101) | VCE(Sat) | Low )       |  |

| 1(1) | 1(0) | vce(sat) | Low         |  |

| 1(1) | 1(1) | re(sat)  | LOW         |  |

The touth table reveal that RTL Grait

functions as NOR gate.

## Advantages:

- +200 wot

- 2) improved speed when compared to DTL

## Disadvantages:

- i) less immunity to noise.

- 2) POOT fam-out capability.

- 3) overall speed is low.

- u) high power dissipation. which can be avoided in DTL

- 2) Direct Coupled transistor logic (DCTL):

- -> Below fig consist of those CE townsistors Q, Q2 and Q3 with collectors tied together.

- -> fan-in is 3 and fan out is 2 sind the output feeds the two transistors By and Q.

- The input to Q, comes directly from the

- output Y' of a previous No'R gate.

- -> Since no registors, capacitors en diodeg and

- used between stages, such a system is

- Called direct-coupled toansistor logic (DCTL).

- -> It also acts as NOR gate.

fig: DCTL as NOR gate

operation:

Condition 1:

All inputs at Low

1-0; V1 = V2 = V3 = 0

The low voltage (V,=0) to an input to Q, comes from saturated saturated toans is too (Q') of a

preceding stage

so,  $V_t = V_{CE(COA)} = V(0)$

sine the current in Q, is almost zero, the output y troise vcc and dy & Q go output y is clamped at into saturation. Hence the output y is clamped at

VBE(sat) = V(1) = 0.7 V. for silicon.

Thus with all inputs in the low state, the output is in high stare.

Condition 23

At least one input v, is in high state.

. i.e; V, = high, V2=V3=0

since Q, is fed from Q', Q' is cut-off and

2, is driven into saturation.

under these circumstances the output y is

Y= VCE(sat) = V(0).

Condition 3:

If more than one input is high, then

the output will costainly be low.

Hence, the NOR function is satisfied.

|          | inpud      | 2          | output    | 108ic state |

|----------|------------|------------|-----------|-------------|

| <u> </u> | <b>V</b> 2 | <b>V</b> 3 | 1         |             |

| 0        | 0          | 0          | Vc C      | High.       |

| 0        | 0          | 1.         | VCE(SOA)  | Low         |

| 0        | 1          | 0          | VCE (SOL) | Low         |

| 0        | . (        | 1          | VCE(SOL)  | Low         |

| \        | 0          | 0          | VCE (SOL) | Low         |

| ,        | 0          | •          | VCE(SOL)  | l ow        |

| •        | •          | 0          | VCE(sax)  | Low         |

|          | 1          |            | VCE(504)  | Low         |

- Advantages:

- ) need for only one low voltage supply (operation . (eldi 2209 21 vz.1 Atic

- 2) Toansistors with low breakdown Voltages may be used.

- 3) The power Dissipation is low

- y) This configuration is used for integrated-circuit manufacture because to ansistors are charper to falsoicate with integrated techniques than 000 808, 124082 en cabaci, 4027.

- Disadvantages:

- ) The reverse saturation arrown for all fan-in transistors adds in the Common Collector- Circuit rosistor Rc.

- so at high temperature, total Eco drop may be large enough so that the output Y is too low to drive the form-out transistors into Saturation:

- 2) Because of Direct Connection, the base Gustand is almost equal to the Collector Curstant

- 2) It suffers from a problem called current hopping i.e., The bages of the fan out transistors are connected together. Since the input characteristics can never be identical.

let us assume by has a much lower NBE for a given ZB than does as. under these circumstances, Qy will hog" most of the base current, and it is possible that as may not even be down into saturation. 3) Diode roomeistor logic (DTL): -> The basic DTL gate act as NAND gate. V(0)=0.24 fig: Two imput NAND gate as DTL &C -> The two inputs of the gate are applied through the diodog DA and DB which are to and mitted to the base of B through diodes D, and Dz. Output of the gate is measured at the collector of 80. -> In this ciscuit, the input dioder along with registor R forms a diode AND gate whose

output is available at point P. The transistor acts as inverter, Thus the output of diode AND gave is invested to gree output of DTL gate of NAND gate.

The transistor & at the output can assume either Low (08) HIGH voltage levels depending whather it operates in saturation en in Cut-off.

> VBE(sat) = 0.9 V for silicon transistor to be in saturation and base arount 28 2cm)

-> From the figure, it is evident that no Hage at point P, Up is responsible to doine the toansistoo & in Cut-off en in saturation.

-> let us calculate the voltage Up at point p, required to doine transistor & into Saturation is

4 (N) = (N) 0, + (N) 02 + (BECCOH) D2

VP(ON) = 0.7+0.7+0.9.

$V_{P(op)} = 2.3 V$

operation:

Condition 1:

when all the impute are high

ie; A = B = V(1) = 5V

so, when all inputs ask high, Dioder DA & DB

will be in off state.

so, Current (I) flows through diodes D, & D2

through base of Q.

we know voltage at point P=2.3V and

voltage 2008 across any of the reverse-biased

input diodes (DA or DB) is 5-2.3 = 2.7V

So, 2.7V is sufficient to keep the input diodep

in remose-biased.

les us calculate the work to Be of Q

$$2_1 = 2 = \frac{vcc - VP}{5K} = \frac{5 - 2.7}{5K} = 0.46mA$$

$$2 = \frac{V_{BC}(sat) - 0}{5k} = \frac{0.9}{5k} = 0.18 \text{ mA}$$

$$2c = \frac{\sqrt{cc - \sqrt{cc (sat)}}}{2.2k} = \frac{5-0.2}{2.2k} = 2.18 \text{ mA}$$

So, toansistoo & to smain in saturation SB> SCCION)

hffmin 20 = 2.18 ~ 8

: If the toansistoo has her larger than & the NAND circuit functions as expected when all the inputs are High.

-1. Y = VCECSOA) = LOW

Condition 2 ;

If at least one input is Low, the output

is expected to 18 High.

let A = V(O), B = V(I)

the diode DA is conducting and DB is Cut-off.

So, voltage at point P is

Vp= V(0) + V0= 0.2+0=7=0.9V

2+ is clear that when up=0.90, the output

toursis too remains in Cut-off and output will

be high.

since to make transistor into saturation,

we need up= 2.3V.

· Y= Vcc = high.

|   | Inpi | us:  | outputs  |             |  |

|---|------|------|----------|-------------|--|

|   | A    | B    | Y        | logic state |  |

|   | v(0) | 1(0) | 100      | high        |  |

| , | V(0) | vci) | Vcc      | high        |  |

|   | VCD  | v(0) | VCC      | high        |  |

|   | 1(1) | 1()  | VCECSON) | LOW         |  |

Advantages:

- i) Emproved noise margin.

- 2) larger fan out

Disadvantage:

- ) speed is slow which can be avoided in TTL

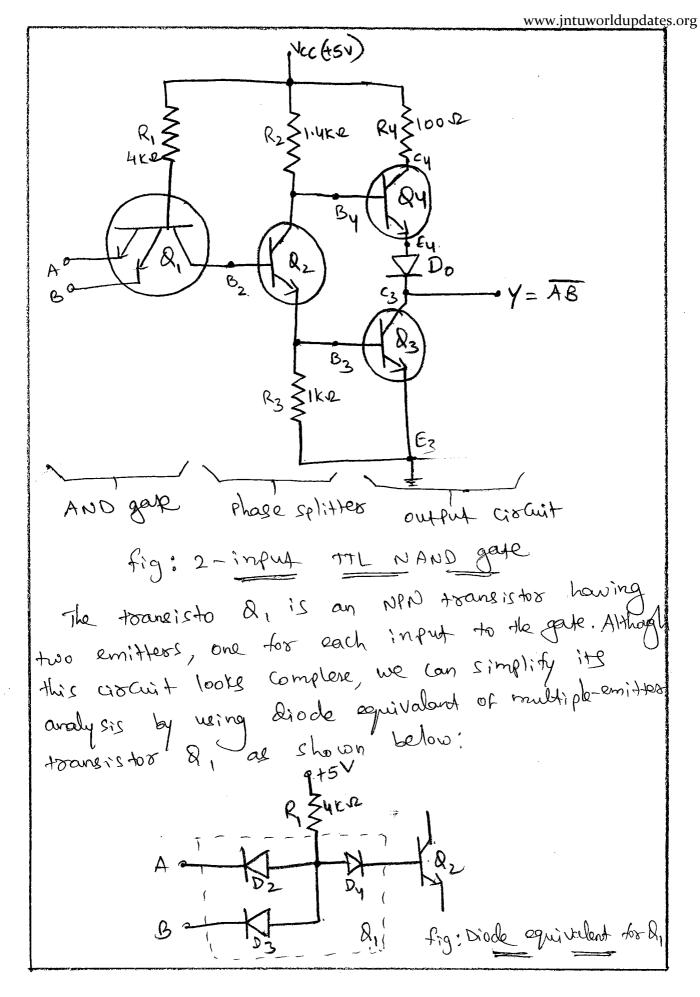

- y) Toansistor-Toansistor logic (TTL):

- -> TIL WOOKS OF NAND gate.

- -> TTL is named for its dependence on transistors alone to perform basic legic eperations.

- -> The circuit diagram of 2-input TTL NAND gate is shown below:

> Diodes Dz y Dz repossent two Emitter-base (E-B) junctions of Q, and Dy is the Collector-base (C-B) junction.

operation:

Condition 1:

when All inputs are high

i.e) A = B = high

diodes D2 9 D3 av senesse-biased, Diode Dy is in forward-biased. The supply voltage Vcc forces a current through oblistor R, and diode

Dy to the base of toansis too d2. This bale

doive is sufficient to two on de

The Collector Current of of of Causes voltage doop across R2 with the result that the potential

at the collector terminal of dz is VCE(sat), which

is not sufficient to make By ON

i. Qy = off.

The emitted current of Q2 supplies necessary base-doine for transistor as & hence as = 00

· output Y = VCE(SOX) = LOW

Condition 2"

when any one input is Low

let A= high, B= low

so diode Dz is off and Dz is on. The supply voltage Va force a current through ssistor R, and diode 03 to the ground.

The potential at Bz is 0.7V (Cut-in voltage of D3). This is not sufficient to twon on toansistoo Q2, since it must overcome both the Patential basoist of Dy and Cut-in voltage of of.

.. Q2 = Off

since &2 is off, there is no base drive

for transistor &3 · . Qz = off

since there is no collector current of d2, point By is quite a high potential which is Sufficient to overcome the cut-in voltage of 84 and barroier potential of Do.

. Qy = 0N

.. output y = high

| Inpu | AS | output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α    | B  | Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0    | 0  | Company of the compan |

| O    | į  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1    | O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •    | •  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

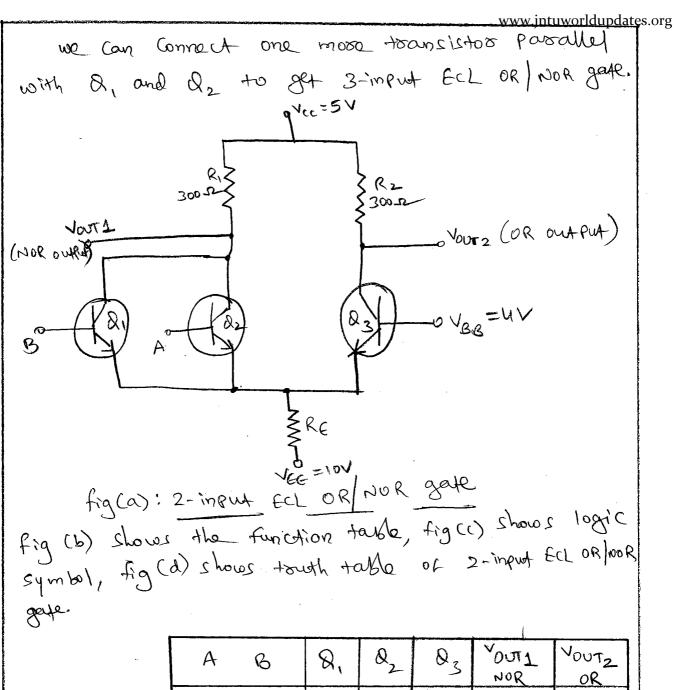

-> It is also called as avorent mode logic (cm)

→ need:

The TIL family uses transistors operating in the saturation mode. As a sesult their switching speed is limited by the storage delay time into associated with a toansistor that is driven into associated

saturation.

Another logic family has been developed that prevents transistor saturation, therety increasing overall switching speed by using a radically different CIOCUMES Structures Called curosny mode logic (CMI) 2009

Emitter Gupled logic (Ecl).

Unlike TTL & CMOS families, ECL does not Produce a large voltage swing between Low & High levels.

It has small voltage swing less than a volt and it internally switches awarent between two possible Rathe depending on the output State.

Advantages "

- 1) It is the fastest among all logic families.

- 2) Transistors are not allowed to go into complete Saturation and thus eliminoding Storage delays.

- 3) switching toansienAs are less because fouret Supply Current is more stable than in TIL and cmos circuits.

Disadvantages:

- 1) As logic levels one rept close to each others noise margin is reduced and it is difficult

- to achieve good noise immunity. 2) Power Consumption is more because townsistors

- are not completely saturated.

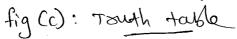

- -> ECL OR NOR GATE:

Below fig(9) shows 2-input ECL OR NOR gave. This has an additional transistor in parallel with

B1.

i) If any input is High Goroegranding toansistor is active, and Vour, is Low(NOR output). At the Same time as is off producing Vourz tight (or output).

| A | 6        | ର,  | 02  | 03  | NOR NOR | VOUT2 |

|---|----------|-----|-----|-----|---------|-------|

| 0 | 0        | off | off | No  | ١       | 0     |

| 0 | 1        | 00  | OFF | OFF | 0       | 1     |

| 1 | 0        | off | 01) | off | 0       | 1     |

| 1 | <b>†</b> | 00  | 010 | OFF | 0       | 1     |

fig(b): Function table

| A | B | 1004 (<br>CHOR) | Vout 2<br>(OR) |

|---|---|-----------------|----------------|

| 0 | 0 | 1               | 0              |

| 0 | 1 | 0               | 1              |

| 1 | O | 0               | 1              |

| Ì | 1 | 0               | 1              |

fig(b): logic Symbol

6) cmos logic families:

The basic building blocks in cross logic circuits are mos transistors.

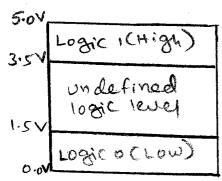

> cmos logic levels:

In general, cross ciscuit may interpret any voltage in the range o to 1.50 of a logic o and in the range 3.5 to 5.00 of a logic 1

The voltages in between 1.5v to 3.5v are not expected to occur except during signal transitions and it they occurs, the circuit may interpret them as either 0 to 1.

STOP ZOM ZOM

A mos toansistos is a those terminal device that acts like a voltage controlled registance.

An input voltage applied to one terminal controls the registance between the remaining terminals.

In cros logic circuits, mos transistor is operated so that its registance is always either very high con nood long.

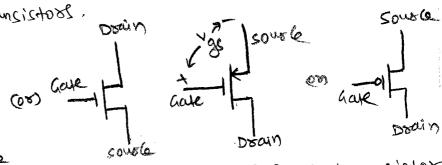

Types of Mos toansistoss:

- i) n-channel (NMOS) and

- 2) P-channel (PMOS)

Bolow fig shows the circuit symbols of NMOS

PMOS toansistors.

consta

80+2i2nort 20MU (a

6) PMOS toansistox

mos transistor has those terminals called gave Source and doain.

NOMOS transistor:

In this, the voltage from gave to source is

normally zero on Positive. If Vgs = 0, then the registance from Joan to Source, Ras is very high. It is of the order of megaohms.

If Vgs = Positive, then Rds is very low-It

is between 0-10 ohms.

PMOS transistor:

In this vge is normally zero or negative. It vgs = 0, then Rds is very high 21 vgg=negative, then Rds is very 100

> Those characteristics of NMOS and PMOS transistal make them use as a switch in digital Ec technology

-> The gate of the mos toansistoo is separated from doain and source by an insulading material with a very high registance. The Voltage applied at gate terminal coreates an electoic field that enhances consetands the

flow of current between source and drain. Due to this effect the mos transistor is also known as mosfet (metal oxide SemiConductor field effect toansistor).

-> The NMOS and PMOS transistors are used together in a complementary way to form cros (complementary Metal oxide semi conductors) logic.

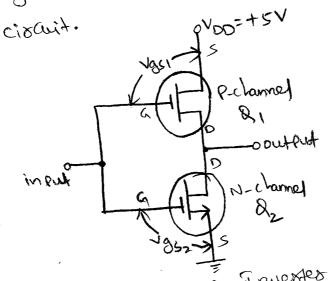

Basic CMOS Zinverter circuit:

-> fig (a) below shows the basic cmos investes

fig (a): c Mos Enverter circuit >It consists of two mosfets in society in such a way that the p-channel device has its source Connected to tupp (a positive voltage) and N-channel device has its source connected to ground.

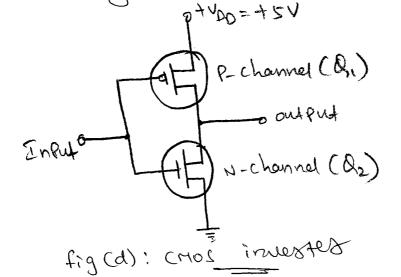

-> The gates of the two devices are connected together as the Common input and drains are connected together as the common output. e) when input is HIGH The gate of Q, (P-channel) is at or slative to source of Q, i.e; vgs,=ov, Thus Q, is off. on the other hand, the gate of & (N-channel) is at tupo selative to its source le; vgs, =two. Thus Q2 is ON. This will produce Vout ~ou as shown in fig(b). figcc): Input = P fig (b): Enput =1 ii) when input is low The gare of Q (P-channel) is at regative Potential relative to its source while le hay Ngg=OV. Thug Q, is ON and Q2 is OFF. This produces output voltage approximately tupp of shown in Ag Co).

| T | A | ۵,  | 0   | output |

|---|---|-----|-----|--------|

| Ì | 0 | 00  | off | \      |

| į | \ | off | 00) | 0      |

Tough table

-> fig (d) shows different symbols used for P-channel and n-channel transistors to reflect their logical behaviour.

The n-channel transistor (Q2) is switched 'ON'

when a HIGH voltage is applied at the input.

The P-channel transistor (8.) has the opposite behaviour, it is switched on when a Low voltage is applied at the input. It is indicated by placing bubble in the Symbol.

Logic symbol.

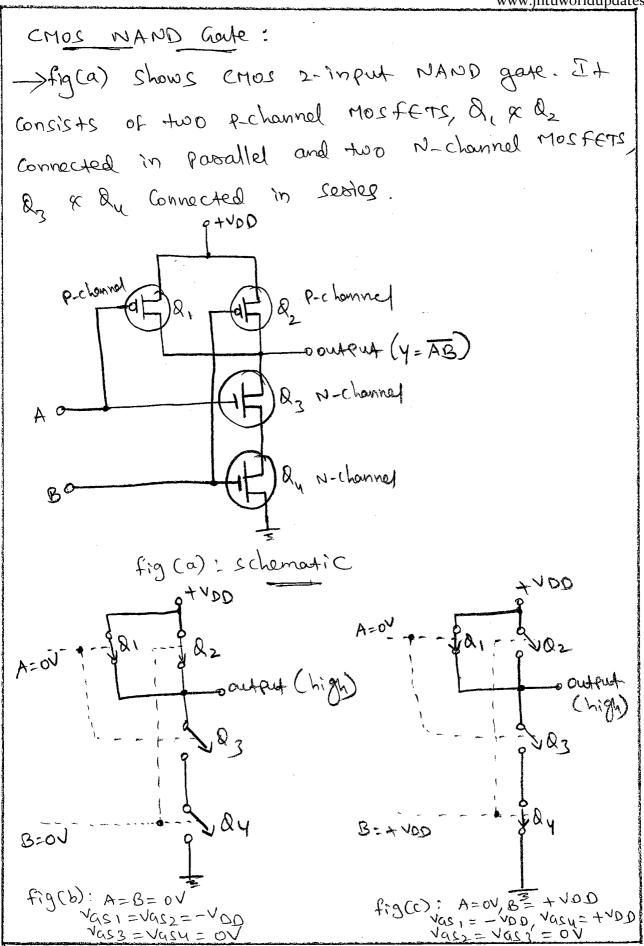

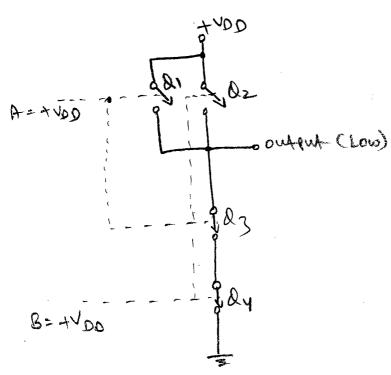

fig(d): A= B = VDD vasi = Vasz = ov Vas3 = Vasu= + VDD

Ifig (b) shows the equivalent switching circuit when both inputs are low. Here, the gates of both pechannel MOSFETS are negative with respect to their source, Since the sources are connected to tVDO. Thus, Q, ir de are both ON. Since the gate-to-source voltages of 83 & By (n-channel mosfers) are both ov, those

Mosfets as off. The output is therefore Connected to AVDD (HIGH) through Q, and Qz and is Disconnected from ground.

when A=0 and B=+VOD. En this case, Q, is one because Vas;=-VoD and Qu is ON because Vas;=-VoD and Qu is ON because Vas;=-VoD and Qu is ON because Vasy=+VDD. MOSFETS Q2 4 Q3 as off because their gase-to-source voltages are ov. Since Q, is on and Q3 is off, the output is Connected to the output is Connected to the output is and the output is connected to the output is and the output is connected to the output is connected to

when  $A = + V_{OD}$  and B = OV, the situation is similar, the output is connected to  $+ V_{OD}$  through  $Q_2$  and it is disconnected from ground because  $Q_1$  is off.

-> fig (d) shows the equivalent switching circuit when both inputs are high (A=B=+VOD), when both inputs are both off and of roly mosfers &, & &2 are both off and of roly

ous both on.

Thus, the output is connected to ground through  $d_3$  or  $d_4$  and it is disconnected

from + VDD.

| A              | В | &,  | Q <sub>2</sub> | 03  | By 1 | output |

|----------------|---|-----|----------------|-----|------|--------|

| 0              | 0 | ON  | 00             | off | oft  | •      |

| 0              | 1 | 010 | 0 4            | off | 00   | •      |

| \              | O | off | ON             | 00  | OFF  | · ·    |

| and the second | 1 | off | off            | 00  | ON   | 0      |

respect to its source.

CMOS NOR gate:

$\rightarrow$  fig (a) shows 2-input cmos NOR gate. Here,  $\rho$ -channel mosfets  $Q_1$  and  $Q_2$  are connected in sories and  $Q_3$  and  $Q_4$  are channel mosfets  $Q_3$  and  $Q_4$  are connected in parallel.

<u>www.intuworldupdate</u>s.org

Like NAND circuit, this circuit can be analyzed by realizing that a Low at any input turns on its corresponding p-channel mosfet and turns off its corresponding mosfet and turns off its corresponding machannel mosfet and vice versa for a high input. This is shown in below fig: